- 您现在的位置:买卖IC网 > PDF目录98252 > TLV2553IDWR (TEXAS INSTRUMENTS INC) 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 PDF资料下载

参数资料

| 型号: | TLV2553IDWR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | ADC |

| 英文描述: | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| 封装: | GREEN, PLASTIC, SOIC-20 |

| 文件页数: | 28/29页 |

| 文件大小: | 603K |

| 代理商: | TLV2553IDWR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页

TLV2553

SLAS354B – SEPTEMBER 2001 – REVISED SEPTEMBER 2002

8

www.ti.com

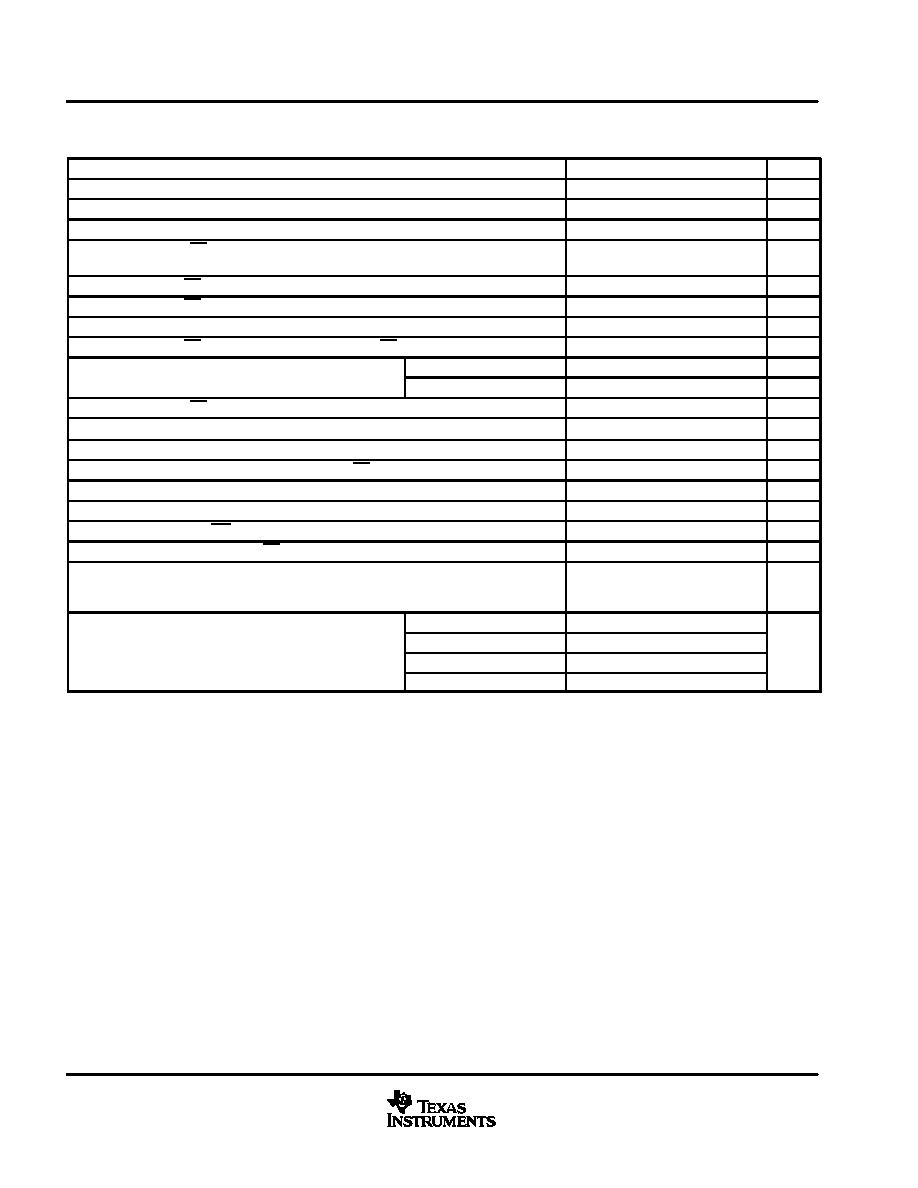

timing characteristics over recommended operating free-air temperature range, VREF+ = 2.5 V,

I/O CLOCK frequency = 10 MHz, VCC = 2.7 V, load = 25 pF (unless otherwise noted)

PARAMETER

MIN

TYP

MAX

UNIT

tw1

Pulse duration I/O CLOCK high or low

40

100000

ns

tsu1

Setup time DATA IN valid before I/O CLOCK rising edge (see Figure 26)

22

ns

th1

Hold time DATA IN valid after I/O CLOCK rising edge (see Figure 26)

0

ns

tsu2

Setup time CS low before first rising I/O CLOCK edge

(see Note 7 and Figure 27)

33

ns

th2

Hold time CS pulse duration high time (see Figure 27)

100

ns

th3

Hold time CS low after last I/O CLOCK falling edge (see Figure 27)

0

ns

th4

Hold time DATA OUT valid after I/O CLOCK falling edge (see Figure 28)

2

ns

th5

Hold time CS high after EOC rising edge when CS is toggled (see Figure 31)

0

ns

td1

Delay time CS falling edge to DATA OUT valid

Load = 25 pF

30

ns

td1

yg

g

(MSB or LSB) (see Figure 25)

Load = 10 pF

22

ns

td2

Delay time CS rising edge to DATA OUT high impedance (see Figure 25)

10

ns

td3

Delay time I/O CLOCK falling edge to next DATA OUT bit valid (see Figure 28)

2

33

ns

td4

Delay time Last I/O CLOCK falling edge to EOC falling edge

75

ns

td5

Delay time last I/O CLOCK falling edge to CS falling edge to abort conversion

1.5

s

tt1

Transition time I/O CLOCK (see Note 7 and Figure 28)

1

s

tt2

Transition time DATA OUT (see Figure 28)

5

ns

tt3

Transition time INT/EOC, CL at 7 pF (see Figure 30)

4

ns

tt4

Transition time DATA IN, CS

10

s

tcycle

Total cycle time (sample, conversion and delays) (see Note 7)

MAX(tconvert) +

I/O period

(8/12/16 CLKs)

s

Source impedance = 25

800

t

l

Channel acquisition time (sample), at 1 k

Source impedance = 100

850

ns

tsample

q(

),

See Figures 33–38 and Note 7

Source impedance = 500

1000

ns

Source impedance = 1 k

1600

NOTE 7: I/O CLOCK period = 8X [1/(I/O CLOCK frequency)] or 12X [1/(I/O CLOCK frequency)] or 16X [1/(I/O CLOCK frequency)] depends on

I/O format selected.

相关PDF资料 |

PDF描述 |

|---|---|

| TLV2553IDWRQ1 | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2556IDWRG4 | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2556IPW | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2556IDWR | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2556IPWR | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TLV2553IDWRG4 | 功能描述:模数转换器 - ADC 12-Bit 200 KSPS 11 Ch Lo-Pwr RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLV2553IDWRQ1 | 功能描述:模数转换器 - ADC Auto Cat 12B 200KSPS 11Ch Low-Pwr Ser ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLV2553IPW | 功能描述:模数转换器 - ADC 12-Bit 200 KSPS 11 Ch Lo-Pwr RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLV2553IPWG4 | 功能描述:模数转换器 - ADC 12-Bit 200 KSPS 11 Ch Lo-Pwr RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| TLV2553IPWR | 功能描述:模数转换器 - ADC 12-Bit 200 KSPS 11 Ch Lo-Pwr RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。