- 您现在的位置:买卖IC网 > PDF目录19342 > TMS320C6415TGLZ7 (Texas Instruments)IC DSP FIXED-POINT 532-FCBGA PDF资料下载

参数资料

| 型号: | TMS320C6415TGLZ7 |

| 厂商: | Texas Instruments |

| 文件页数: | 12/146页 |

| 文件大小: | 0K |

| 描述: | IC DSP FIXED-POINT 532-FCBGA |

| 标准包装: | 60 |

| 系列: | TMS320C6414T/15T/16T |

| 类型: | 定点 |

| 接口: | 主机接口,McBSP,PCI,UTOPIA |

| 时钟速率: | 720MHz |

| 非易失内存: | 外部 |

| 芯片上RAM: | 1.03MB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.20V |

| 工作温度: | 0°C ~ 90°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 532-BFBGA,FCBGA |

| 供应商设备封装: | 532-FCBGA(23x23) |

| 包装: | 托盘 |

| 配用: | TMDXEVM6452-ND - TMDXEVM6452 296-23038-ND - DSP STARTER KIT FOR TMS320C6416 |

| 其它名称: | 296-17756 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页

TMS320C6414T, TMS320C6415T, TMS320C6416T

FIXEDPOINT DIGITAL SIGNAL PROCESSORS

SPRS226M NOVEMBER 2003 REVISED APRIL 2009

109

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

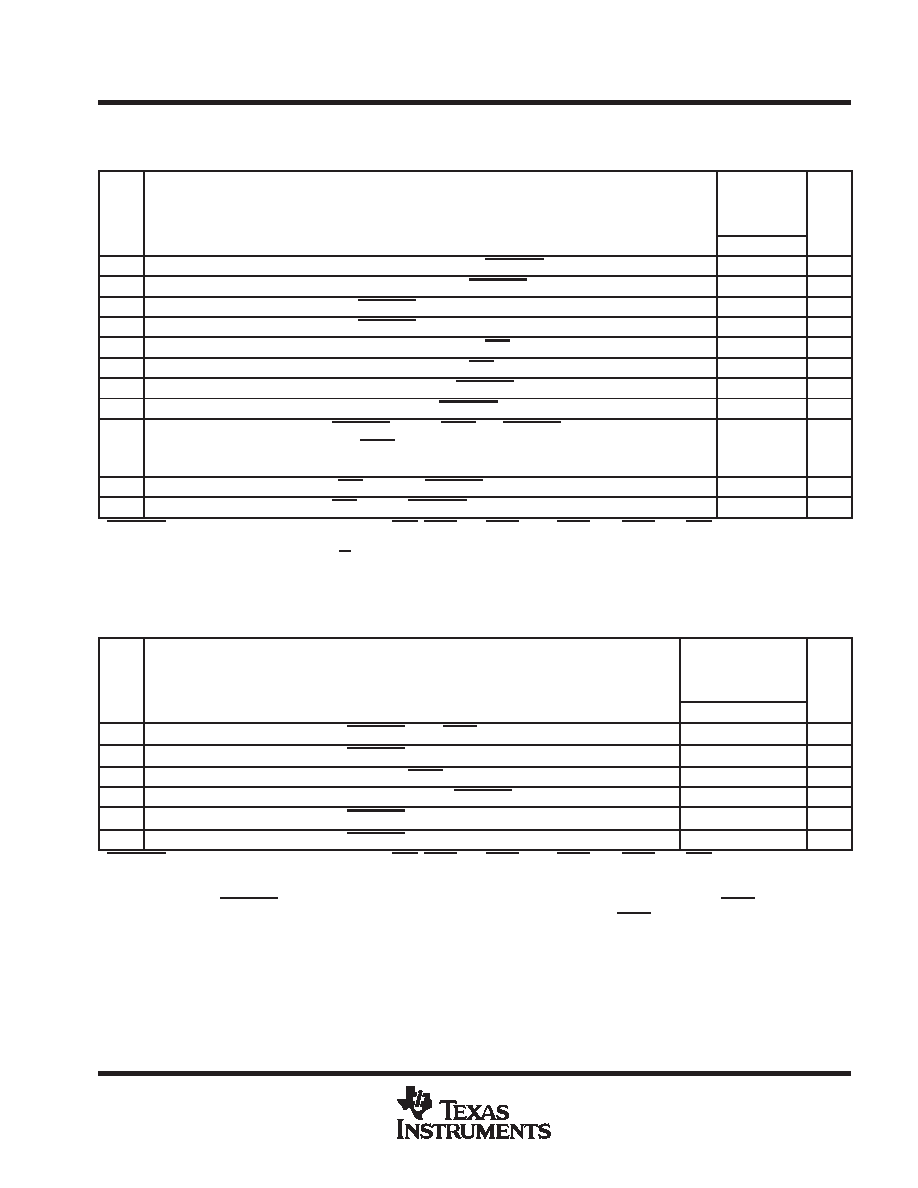

HOST-PORT INTERFACE (HPI) TIMING

timing requirements for host-port interface cycles (see Figure 39 through Figure 46)

NO.

600

850

720

1G

UNIT

MIN

MAX

1

tsu(SELV-HSTBL)

Setup time, select signals§ valid before HSTROBE low

5

ns

2

th(HSTBL-SELV)

Hold time, select signals§ valid after HSTROBE low

2.4

ns

3

tw(HSTBL)

Pulse duration, HSTROBE low

4P

ns

4

tw(HSTBH)

Pulse duration, HSTROBE high between consecutive accesses

4P

ns

10

tsu(SELV-HASL)

Setup time, select signals§ valid before HAS low

5

ns

11

th(HASL-SELV)

Hold time, select signals§ valid after HAS low

2

ns

12

tsu(HDV-HSTBH)

Setup time, host data valid before HSTROBE high

5

ns

13

th(HSTBH-HDV)

Hold time, host data valid after HSTROBE high

2.8

ns

14

th(HRDYL-HSTBL)

Hold time, HSTROBE low after HRDY low. HSTROBE should not be

inactivated until HRDY is active (low); otherwise, HPI writes will not complete

properly.

2

ns

18

tsu(HASL-HSTBL)

Setup time, HAS low before HSTROBE low

2

ns

19

th(HSTBL-HASL)

Hold time, HAS low after HSTROBE low

2.1

ns

HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.

P = 1/CPU clock frequency in ns. For example, when running parts at 720 MHz, use P = 1.39 ns.

§ Select signals include: HCNTL[1:0] and HR/W. For HPI16 mode only, select signals also include HHWIL.

Select the parameter value of 4P or 12.5 ns, whichever is greater.

switching characteristics over recommended operating conditions during host-port interface

cycles (see Figure 39 through Figure 46)

NO.

PARAMETER

600

850

720

1G

UNIT

MIN

MAX

6

td(HSTBL-HRDYH)

Delay time, HSTROBE low to HRDY high#

1.3

4P + 8

ns

7

td(HSTBL-HDLZ)

Delay time, HSTROBE low to HD low impedance for an HPI read

2

ns

8

td(HDV-HRDYL)

Delay time, HD valid to HRDY low

3

ns

9

toh(HSTBH-HDV)

Output hold time, HD valid after HSTROBE high

1.5

ns

15

td(HSTBH-HDHZ)

Delay time, HSTROBE high to HD high impedance

12

ns

16

td(HSTBL-HDV)

Delay time, HSTROBE low to HD valid (HPI16 mode, 2nd half-word only)

4P + 8

ns

HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.

P = 1/CPU clock frequency in ns. For example, when running parts at 720 MHz, use P = 1.39 ns.

# This parameter is used during HPID reads and writes. For reads, at the beginning of a word transfer (HPI32) or the first half-word transfer (HPI16)

on the falling edge of HSTROBE, the HPI sends the request to the EDMA internal address generation hardware, and HRDY remains high until

the EDMA internal address generation hardware loads the requested data into HPID. For writes, HRDY goes high if the internal write buffer is

full.

相关PDF资料 |

PDF描述 |

|---|---|

| ASM24DSAS | CONN EDGECARD 48POS R/A .156 SLD |

| A54SX16A-PQG208 | IC FPGA 180I/O 208PQFP |

| R12P215D/P/R6.4 | CONV DC/DC 2W 12VIN +/-15VOUT |

| GBM08DSEH | CONN EDGECARD 16POS .156 EYELET |

| 745967-7 | CONN D-SUB RCPT STR 25POS PCB AU |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TMS320C6415TGLZ8 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| TMS320C6415TGLZA6 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| TMS320C6415TGLZA7 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMS320C6415TGLZA8 | 制造商:TI 制造商全称:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMS320C6415TGLZWA8 | 制造商:Texas Instruments 功能描述: |

发布紧急采购,3分钟左右您将得到回复。