- 您现在的位置:买卖IC网 > PDF目录382627 > TMX320R2812PBKS (Texas Instruments, Inc.) TMS320R2811, TMS320R2812 Digital Signal Processors PDF资料下载

参数资料

| 型号: | TMX320R2812PBKS |

| 厂商: | Texas Instruments, Inc. |

| 元件分类: | 数字信号处理 |

| 英文描述: | TMS320R2811, TMS320R2812 Digital Signal Processors |

| 中文描述: | TMS320R2811,TMS320R2812数字信号处理器 |

| 文件页数: | 20/147页 |

| 文件大小: | 2021K |

| 代理商: | TMX320R2812PBKS |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页

Introduction

20

June 2004

SPRS257

Table 2

2. Signal Descriptions

(Continued)

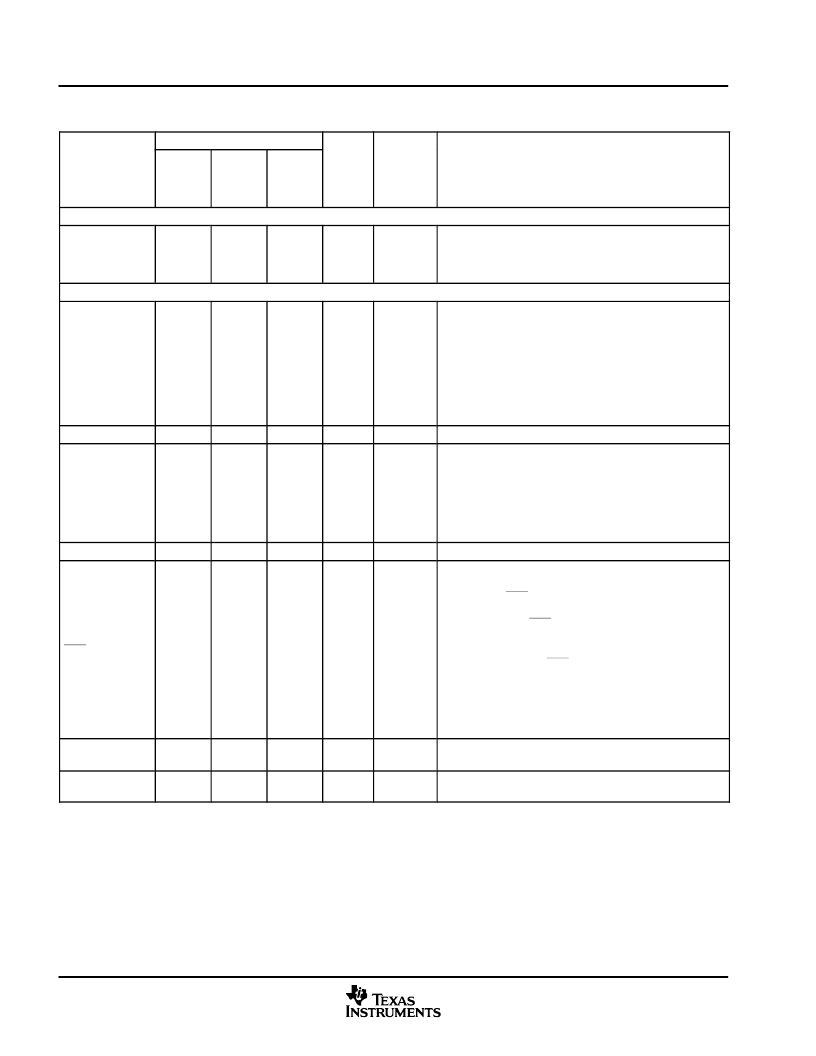

NAME

DESCRIPTION

PU/PD

§

I/O/Z

PIN NO.

128-PIN

PBK

176-PIN

PGF

179-PIN

GHH

AND

ZHH

XINTF SIGNALS (2812 ONLY) (CONTINUED)

XREADY

B6

161

I

PU

Ready Signal. Indicates peripheral is ready to complete the

access when asserted to 1. XREADY can be configured to be

a synchronous or an asynchronous input. See the timing

diagrams for more details.

JTAG AND MISCELLANEOUS SIGNALS

X1/XCLKIN

K9

77

58

I

Oscillator Input

input to the internal oscillator. This pin is also

used to feed an external clock. The 28x can be operated with

an external clock source, provided that the proper voltage

levels be driven on the X1/XCLKIN pin. It should be noted that

the X1/XCLKIN pin is referenced to the 1.8-V (or 1.9-V) core

digital power supply (V

DD

), rather than the 3.3-V I/O supply

(V

DDIO

). A clamping diode may be used to clamp a buffered

clock signal to ensure that the logic-high level does not

exceed V

DD

(1.8 V or 1.9 V) or a 1.8-V oscillator may be used.

Oscillator Output

Output clock derived from SYSCLKOUT to be used for

external wait-state generation and as a general-purpose clock

source. XCLKOUT is either the same frequency, 1/2 the

frequency, or 1/4 the frequency of SYSCLKOUT. At reset,

XCLKOUT = SYSCLKOUT/4. The XCLKOUT signal can be

turned off by setting bit 3 (CLKOFF) of the XINTCNF2 register

to 1.

X2

M9

76

57

O

XCLKOUT

F11

119

87

O

TESTSEL

A13

134

97

I

PD

Test Pin. Reserved for TI. Must be connected to ground.

Device Reset (in) and Watchdog Reset (out).

XRS

D6

160

113

I/O

PU

Device reset. XRS causes the device to terminate execution.

The PC will point to the address contained at the location

0x3FFFC0. When XRS is brought to a high level, execution

begins at the location pointed to by the PC. This pin is driven

low by the DSP when a watchdog reset occurs. During

watchdog reset, the XRS pin will be driven low for the

watchdog reset duration of 512 XCLKIN cycles.

The output buffer of this pin is an open-drain with an internal

pullup (100

μ

A, typical). It is recommended that this pin be

driven by an open-drain device.

TEST1

M7

67

51

I/O

This pin is a “no connect (NC)” (i.e., this pin is not connected

to any circuitry internal to the device).

TEST2

N7

66

50

I/O

This pin is a “no connect (NC)” (i.e., this pin is not connected

to any circuitry internal to the device).

Typical drive strength of the output buffer for all pins is 4 mA except for TDO, XCLKOUT, XF, XINTF, EMU0, and EMU1 pins, which are 8 mA.

I = Input, O = Output, Z = High impedance

§

PU = pin has internal pullup; PD = pin has internal pulldown

A

相关PDF资料 |

PDF描述 |

|---|---|

| TMX320R2812PGFA | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320R2812PGFQ | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320R2812PGFS | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320R2812ZHHA | TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320R2812ZHHQ | TMS320R2811, TMS320R2812 Digital Signal Processors |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TMX320R2812PGFA | 制造商:TI 制造商全称:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320R2812PGFQ | 制造商:TI 制造商全称:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320R2812PGFS | 制造商:TI 制造商全称:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320R2812ZHHA | 制造商:TI 制造商全称:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

| TMX320R2812ZHHQ | 制造商:TI 制造商全称:Texas Instruments 功能描述:TMS320R2811, TMS320R2812 Digital Signal Processors |

发布紧急采购,3分钟左右您将得到回复。