- 您现在的位置:买卖IC网 > PDF目录68613 > TPS60252RTET (TEXAS INSTRUMENTS INC) 0.65 A SWITCHED CAPACITOR CONVERTER, 750 kHz SWITCHING FREQ-MAX, PQCC16 PDF资料下载

参数资料

| 型号: | TPS60252RTET |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 稳压器 |

| 英文描述: | 0.65 A SWITCHED CAPACITOR CONVERTER, 750 kHz SWITCHING FREQ-MAX, PQCC16 |

| 封装: | 3 X 3 MM, GREEN, PLASTIC, QFN-16 |

| 文件页数: | 19/25页 |

| 文件大小: | 762K |

| 代理商: | TPS60252RTET |

www.ti.com............................................................................................................................................................ SLVS769C – APRIL 2007 – REVISED APRIL 2008

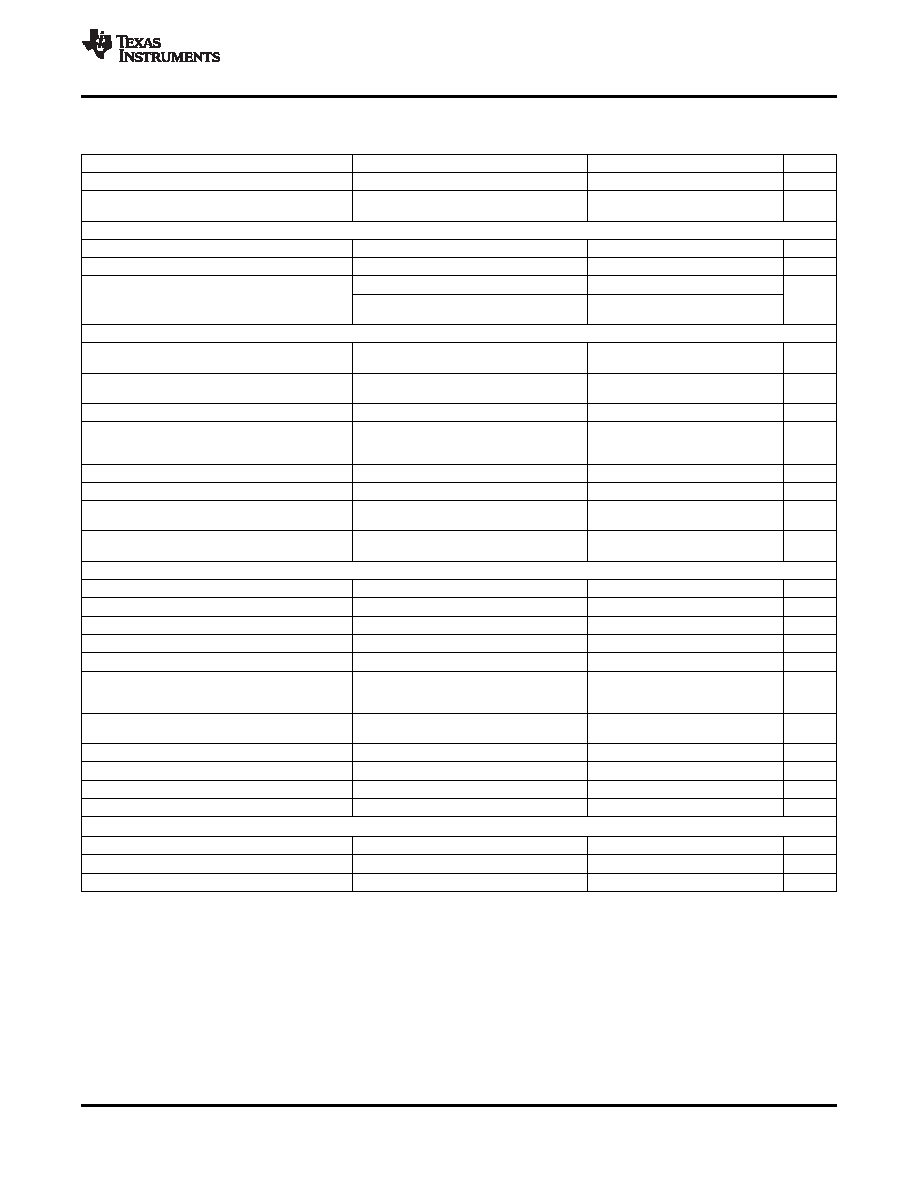

ELECTRICAL CHARACTERISTICS (continued)

VI = 3.5 V, TA = –40°C to 85°C, typical values are at TA = 25°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Vhys

Under-voltage lockout hysterisis

UVLO1

210

mV

VI = 3 V, CO = 1 F,

TS

Soft start time(3)

0.5

ms

IMAIN_LED = 15 mA × 4

CHARGE PUMP

Vout

Overvoltage limit

6.5

V

Fs

Switching frequency

750

kHz

×1 Mode, (V

I –VO)/IO

1.2

RO

Open loop output impedance

×1.5 Mode, (V

I × 1.5 – VO)/IO VI = 3.0V (IO =

3.5

5.0

120 mA)

CURRENT SINK

Current matching of sub LEDs at light

ISUB_LED = 100 A × 2, VDXX = 0.4 V

Km_sub

0

±2%

load condition(4)

IMAIN_LED = 15 mA × 4,

Km_main

LED to LED Current matching(5)

±0.1%

±5%

3.0 V

≤ VI ≤ 4.2 V

Ka

Current accuracy

ILED = 15 mA

±7%

Main and Sub Display Current Register =

Maximum LED current of DM1-4 and

ID_MS

0

×01&2(111111),

25.5

mA

DS1-2

VDXX = 0.2 V

ID_DM5

Maximum LED current of DM5

Aux Display Current Register = 0

×03 (XXXX11)

80

mA

VDropOut

LED Drop out voltage

See (6)

80

120

mV

1

× Mode to 1.5× mode transition

VDXX Falling, 15 mA × 4 measured on the

VTH_GU

85

100

120

mV

threshold voltage(7)

lowest VDXX

Input voltage hysteresis for 1.5

× to 1×

Measured as VI – (VO – VDXX_MIN), IMAIN_LED =

VTH_GD

550

mV

mode transition

15 mA

× 4

SERIAL INTERFACE TIMING REQUIREMENTS

fmax

Clock frequency

400

kHz

twH(HIGH)

Pulse duration, clock high time

600

ns

twL(LOW)

Pulse duration, clock low time

1300

ns

tr

DATA and CLK rise time

300

ns

tf

DATA and CLK fall time

300

ns

High time (repeated) START

th(STA)

condition(after this period the first clock

600

ns

pulse is generated)

Setup time for repeated START

tsu(STA)

600

ns

condition

th(DATA)

Data input hold time

0

ns

tsu(DATA)

Data input setup time

100

ns

tsu(STO)

STOP condition setup time

600

ns

t(BUF)

Bus free time

1300

ns

I2C COMPATIBLE INTERFACE VOLTAGE SPECIFICATION (SCLK, SDAT, VIO)

VIL

Low-leveI input voltage

3.0 V

≤ VI ≤ 6.0 V

0

0.5

V

VIH

High-level input voltage

3.0 V

≤ VI ≤ 6.0 V

1.1

V

VOL

Low-level output voltage

ILOAD = 2 mA

0.4

V

(3)

Measurement Condition: From enabling the LED driver to 90% output voltage after VI is already up.

(4)

LED current matching is defined as: (ISUB_LED_WORST – IAVG_SUB) / IAVG_SUB

(5)

LED to LED Current Matching is defined as: (IMAIN_LED_WORST – IAVG_MAIN) / IAVG_MAIN

(6)

Dropout Voltage is defined as VDXX (WLED Cathode) to GND voltage at which current into the LED drops 10% from the LED current at

VDXX = 0.2 V, WLED current = 15 mA × 4.

(7)

As VI drops, VDXX eventually falls below the switchover threshold of 100mV, and TPS60250/2 switches to 1.5× mode. See the Operating

Principle section for details about the mode transition thresholds.

Copyright 2007–2008, Texas Instruments Incorporated

3

相关PDF资料 |

PDF描述 |

|---|---|

| TPS61097-33DBVT | 0.475 A BATTERY CHARGE CONTROLLER, PDSO5 |

| TPS61097-18DBVR | 0.475 A BATTERY CHARGE CONTROLLER, PDSO5 |

| TPS61097-01DBVT | 0.475 A BATTERY CHARGE CONTROLLER, PDSO6 |

| TPS61097-50DBVR | 0.475 A BATTERY CHARGE CONTROLLER, PDSO5 |

| TPS61097-18DBVT | 0.475 A BATTERY CHARGE CONTROLLER, PDSO5 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TPS60252RTETG4 | 功能描述:LED照明驱动器 Hi Eff Charge Pump for 7 WLEDs RoHS:否 制造商:STMicroelectronics 输入电压:11.5 V to 23 V 工作频率: 最大电源电流:1.7 mA 输出电流: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:SO-16N |

| TPS60255 | 制造商:TI 制造商全称:Texas Instruments 功能描述:HIGH EFFICIENCY CHARGE PUMP FOR 7 WLEDs DRIVER WITH 1 WIRE INTERFACE |

| TPS60255EVM-262 | 功能描述:电源管理IC开发工具 TPS60255EVM-262 EVAL MOD RoHS:否 制造商:Maxim Integrated 产品:Evaluation Kits 类型:Battery Management 工具用于评估:MAX17710GB 输入电压: 输出电压:1.8 V |

| TPS60255RTER | 功能描述:LED照明驱动器 7Ch High Eff 175 mA Charge Pump RoHS:否 制造商:STMicroelectronics 输入电压:11.5 V to 23 V 工作频率: 最大电源电流:1.7 mA 输出电流: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:SO-16N |

| TPS60255RTERG4 | 功能描述:LED照明驱动器 7Ch Hi Eff 175mA Charge Pump RoHS:否 制造商:STMicroelectronics 输入电压:11.5 V to 23 V 工作频率: 最大电源电流:1.7 mA 输出电流: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:SO-16N |

发布紧急采购,3分钟左右您将得到回复。