- 您现在的位置:买卖IC网 > PDF目录69525 > TRU050-GALCA16.384-8.192 (VECTRON INTERNATIONAL) PHASE LOCKED LOOP, CDSO16 PDF资料下载

参数资料

| 型号: | TRU050-GALCA16.384-8.192 |

| 厂商: | VECTRON INTERNATIONAL |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PHASE LOCKED LOOP, CDSO16 |

| 封装: | HERMETIC SEALED, GULL WING, CERAMIC, SMT, DIP-16 |

| 文件页数: | 2/17页 |

| 文件大小: | 627K |

| 代理商: | TRU050-GALCA16.384-8.192 |

Vectron International 166 Glover Avenue, Norwalk, CT 06856-5160 Tel: 1-88-VECTRON-1 e-mail: vectron@vectron.com

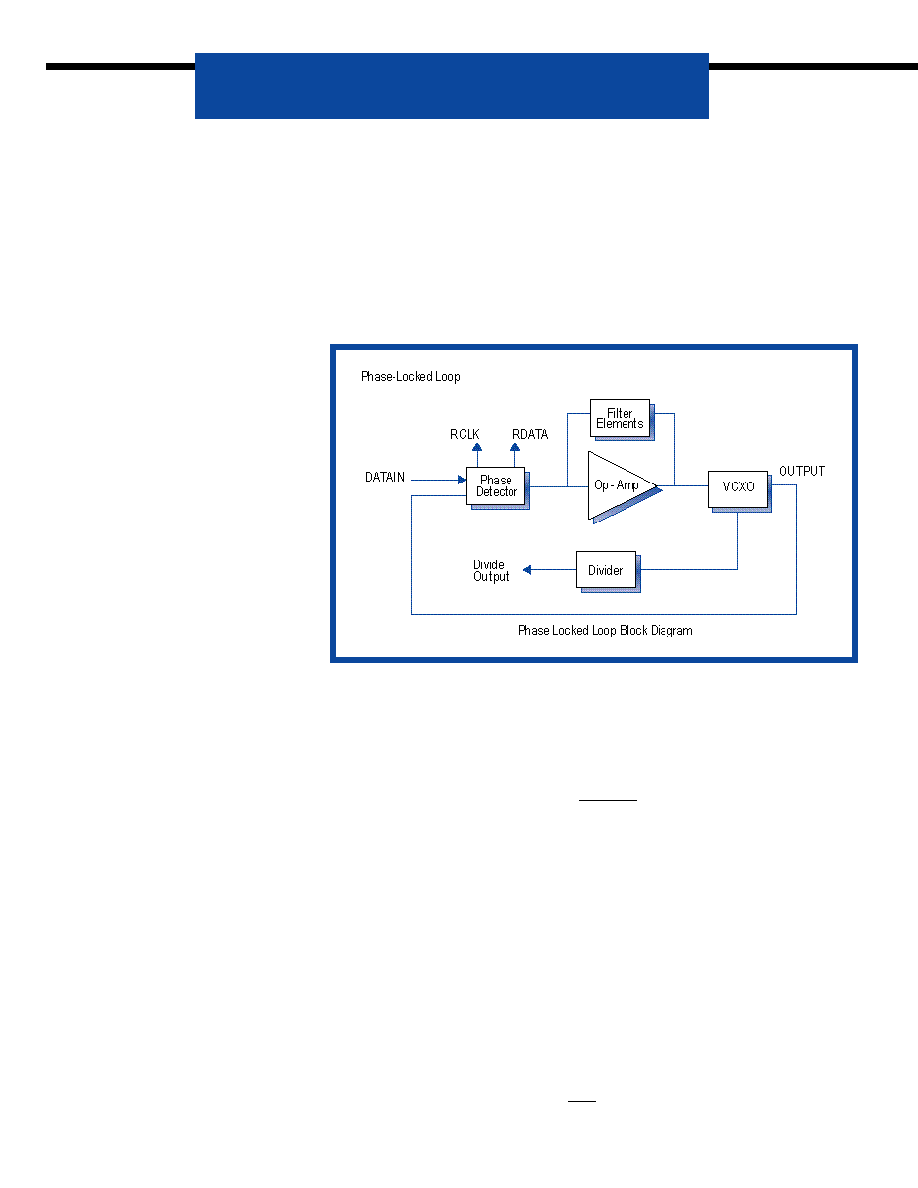

A typical PLL is illustrated in figure 12. Be advised that many textbook equations describing loop dynamics, such as capture range or lockin time, are based on ideal systems.

Such equations may not be accurate for real systems with nonlinearities, DC offsets and noise. A PLL is a feedback system which forces the output frequency to lockin both

phase and frequency to the fundamental frequency of the input signal.

When initially out of lock, the output of the phase detector is proportional to the difference in frequency between the two phase detector inputs. This beat note varies the

output frequency of the VCXO, and in a properly designed phase-locked loop, the loop action forces Vc to the correct value to bring the system into lock.

A designer’s primary concern is to select a loop filter that ensures lockin and stability, while providing adequate

filtering of input signal noise or jitter. An initial design starts with a known DATAIN signal and an output

specification. An initial analysis of the open loop gain response provides insight into the response of the system.

Using figure 12, the open loop gain is:

G(s)= Kp kV AV(s)

sN

Where:

Kp is the phase detector gain in V/rad (-0.53 x Data Density).

kV is the VCXO gain constant in Rad/Vs.

AV(s) is the loop filter transfer function.

N is the divide ratio.

1/s converts the VCXO frequency output to a phase output.

The open loop gain may be plotted and varied using the SPICE model provided in figure 13. The gain, frequency,

and loop filter configurations may be varied to producedesired responses. In the first-order phase-locked loop,

where AV(s) and N equal 1, the gain curve has a 20 dB/decade slope with unity gain at:

f = kV Kp where kV is in rad/Vs.

2

π

Figure 12.

10 of 17

How Does It Perform?

相关PDF资料 |

PDF描述 |

|---|---|

| TRU050-GALHA19.440-9.720 | PHASE LOCKED LOOP, CDSO16 |

| TRU050-GBLGA50.000-12.500 | PHASE LOCKED LOOP, CDSO16 |

| TRU050-TACCA41.2416-20.6208 | PHASE LOCKED LOOP, CDIP16 |

| TRU050-TALCA20.480-10.240 | PHASE LOCKED LOOP, CDIP16 |

| TRU050-GACFA49.152-24.576 | PHASE LOCKED LOOP, CDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TRU050-GALFA | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE DROP IN QUARTZ STABILIZED PLL SOLUTUION |

| TRU050-GALGA | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE DROP IN QUARTZ STABILIZED PLL SOLUTUION |

| TRU050-GALGA-1M0000000 | 制造商:VECTRON 制造商全称:Vectron International, Inc 功能描述:Complete VCXO based Phase-Locked Loop |

| TRU050GALGA-32.000/16.000 | 制造商:Vectron International 功能描述:SINGLE DROP-IN QUARTZ STABILIZED PLL, CDSO16 |

| TRU050-GALGA-65M0000000 | 制造商:VECTRON 制造商全称:Vectron International, Inc 功能描述:Complete VCXO based Phase-Locked Loop |

发布紧急采购,3分钟左右您将得到回复。