- 您现在的位置:买卖IC网 > PDF目录69525 > TRU050-TALCA20.480-10.240 (VECTRON INTERNATIONAL) PHASE LOCKED LOOP, CDIP16 PDF资料下载

参数资料

| 型号: | TRU050-TALCA20.480-10.240 |

| 厂商: | VECTRON INTERNATIONAL |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PHASE LOCKED LOOP, CDIP16 |

| 封装: | HERMETIC SEALED, CERAMIC, DIP-16 |

| 文件页数: | 13/17页 |

| 文件大小: | 627K |

| 代理商: | TRU050-TALCA20.480-10.240 |

Vectron International 166 Glover Avenue, Norwalk, CT 06856-5160 Tel: 1-88-VECTRON-1 e-mail: vectron@vectron.com

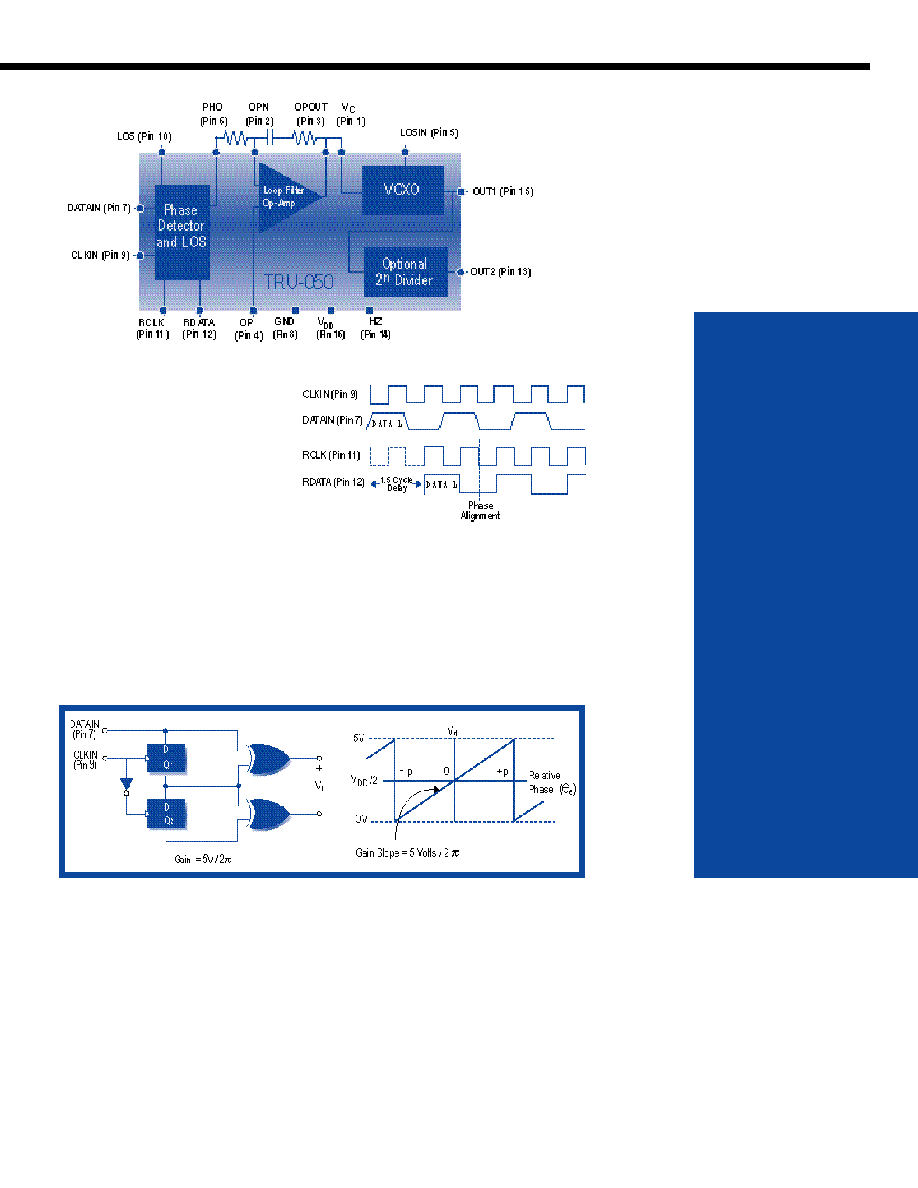

The falling edge of RCLK is coincident with

the center of the regenerated NRZ RDATA

pulse. Figure 6 shows a 1010 data stream

with a 100% data transition density. In

general, this will not be the case and input

data will have fewer data transitions.

However, the phase detector will still seek

to align the falling edge of the RCLK signal with the center of each RDATA pulse.

For applications where the input clock or data signal, DATAIN, is very low in frequency (<200kHz), clock

information may pass through the phase detector because of its finite low pass characteristic. In applications

such as this, an additional pole may be necessary in the loop filter to attenuate these AC components prior to

the VCXO input. Please contact Vectron’s Applications Engineering staff for further detail.

Figure 5.

Figure 7.

Figure 6.

Figure 8.

5 of 17

How is it

manufactured?

The TRU-050 is

assembled in

“state of the art”

class 100 and class

10,000 clean

rooms using leading

edge, high volume

automation equip-

ment and advanced

ASIC technology.

Phase Detector Gain Calculation

The schematic diagram (figure 7) shows a simplified representation of the phase detector's basic error generation function. The actual circuit is more complex and includes

circuitry to reduce the TRU-050's dependence on input data duty-cycle. In general, the TRU-050 is insensitive to duty cycle and duty cycle changes. This circuit provides a

output (VD) DC level which is proportional to the relative phase of DATAIN (Pin 7) and CLKIN (Pin 9). A plot of the output (VD) versus relative phase is shown in figure

8. The slope of the output (VD ) versus relative phase (0e) is 5V/2π.

The phase detector block also includes an output gain stage which should be considered when calculating the gain of the complete phase detector block. This gain stage

has a gain of 2/3, and converts the differential signal to a single-ended DC output.

相关PDF资料 |

PDF描述 |

|---|---|

| TRU050-GACFA49.152-24.576 | PHASE LOCKED LOOP, CDSO16 |

| TRU050-GALGA25.000-12.500 | PHASE LOCKED LOOP, CDSO16 |

| TRU050-GBLGA16.128-4.032 | PHASE LOCKED LOOP, CDSO16 |

| TRU050-GBLHA24.576-6.144 | PHASE LOCKED LOOP, CDSO16 |

| TRU050-GDCCA65.536-4.096 | PHASE LOCKED LOOP, CDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TRU050-TALFA | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE DROP IN QUARTZ STABILIZED PLL SOLUTUION |

| TRU050-TALGA | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE DROP IN QUARTZ STABILIZED PLL SOLUTUION |

| TRU050-TALGA-1M0000000 | 制造商:VECTRON 制造商全称:Vectron International, Inc 功能描述:Complete VCXO based Phase-Locked Loop |

| TRU050-TALGA-65M0000000 | 制造商:VECTRON 制造商全称:Vectron International, Inc 功能描述:Complete VCXO based Phase-Locked Loop |

| TRU050-TALGB-1M0000000 | 制造商:VECTRON 制造商全称:Vectron International, Inc 功能描述:Complete VCXO based Phase-Locked Loop |

发布紧急采购,3分钟左右您将得到回复。