- 您现在的位置:买卖IC网 > PDF目录16115 > TS-MAC-PM-UT4 (Lattice Semiconductor Corporation)SITE LICENSE ETH MAC TRI ECP2M PDF资料下载

参数资料

| 型号: | TS-MAC-PM-UT4 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 25/66页 |

| 文件大小: | 0K |

| 描述: | SITE LICENSE ETH MAC TRI ECP2M |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | TSMACPMUT4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

�� �

�

Lattice� Semiconductor�

�Functional� Description�

�Internal� Registers�

�The� TSMAC� IP� core� internal� registers� are� initialized� through� the� generic� Host� Interface.� These� rules� apply� when�

�accessing� the� internal� registers:�

�?� With� the� 8-bit� Host� Interface,� the� individual� bytes� of� the� registers� are� accessed� through� their� corresponding�

�addresses,� with� the� lower� address� pointing� to� the� lower� byte.�

�?� The� reserved� bits� should� be� programmed� to� 0.� These� bits� are� invalid,� and� should� be� discarded� when� read.�

�?� All� registers� except� the� MODE� and� GMII� Management� registers� can� be� written� into� only� when� the� core� is� dis-�

�abled,� i.e.,� MAC� is� in� the� IDLE� state� (Tx_en� and� Rx_en� low� in� the� MODE� register).� The� MODE� and� GMII� Man-�

�agement� registers� are� the� only� registers� that� can� be� written� to� after� the� TSMAC� IP� core� is� no� longer� disabled.�

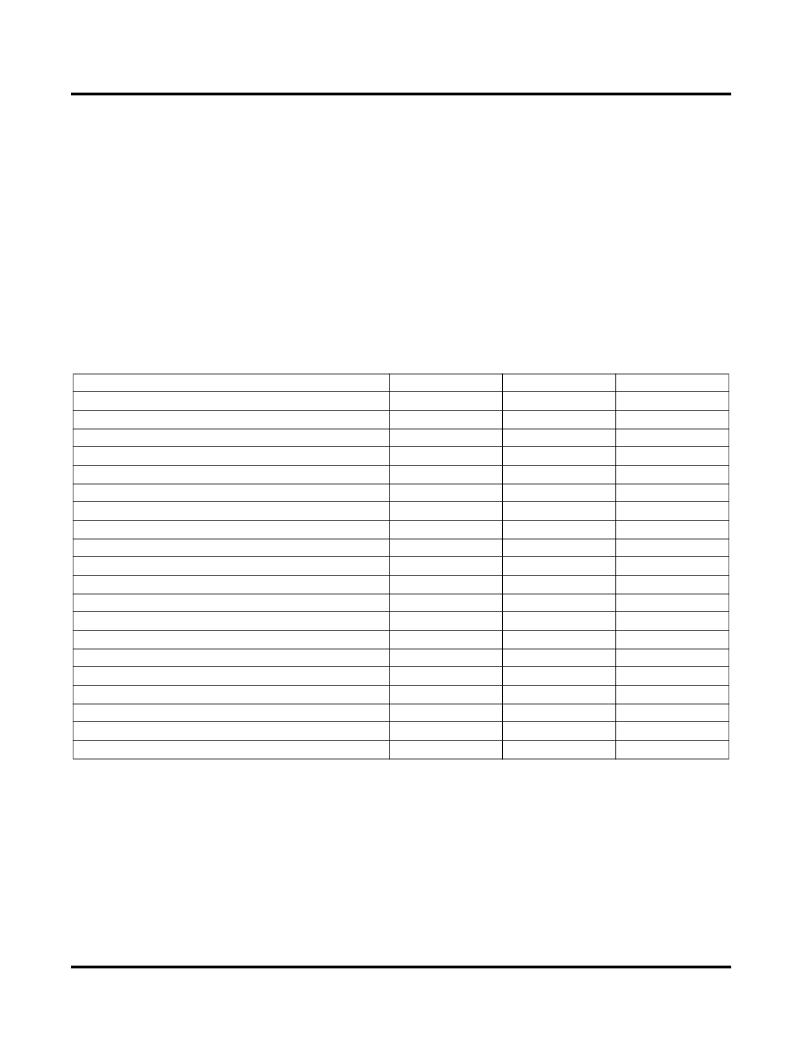

�Table� 2-4� lists� the� TSMAC� IP� core� registers� accessible� via� the� Host� Interface.� The� registers� are� either� Read/Write�

�(R/W)� or� Read� Only� (RO)� for� status� reporting� purposes.� The� values� of� the� registers� immediately� after� the� Reset�

�Condition� is� removed� from� the� TSMAC� IP� core� (POR� Value� in� Hexadecimal� format)� are� also� given.�

�Table� 2-4.� TSMAC� IP� Core� Internal� Registers�

�Register� Description�

�Mode� register�

�Transmit� and� Receive� Control� register�

�Maximum� Packet� Size� register�

�Inter-Packet� Gap� register�

�TSMAC� IP� core� Address� register� 0�

�TSMAC� IP� core� Address� register� 1�

�TSMAC� IP� core� Address� register� 2�

�Transmit� and� Receive� Status�

�GMII� Management� Interface� Control� register�

�GMII� Management� Data� register�

�VLAN� Tag� Length/type� register�

�Multicast_table_0�

�Multicast_table_1�

�Multicast_table_2�

�Multicast_table_3�

�Multicast_table_4�

�Multicast_table_5�

�Multicast_table_6�

�Multicast_table_7�

�Pause_opcode�

�Mnemonic�

�MODE�

�TX_RX_CTL�

�MAX_PKT_SIZE�

�IPG_VAL�

�MAC_ADDR_0�

�MAC_ADDR_1�

�MAC_ADDR_2�

�TX_RX_STS�

�GMII_MNG_CTL�

�GMII_MNG_DAT�

�VLAN_TAG�

�MLT_TAB_0�

�MLT_TAB_1�

�MLT_TAB_2�

�MLT_TAB_3�

�MLT_TAB_4�

�MLT_TAB_5�

�MLT_TAB_6�

�MLT_TAB_7�

�PAUS_OP�

�I/O� Address�

�00H� -� 01H�

�02H� -� 03H�

�04H� -� 05H�

�08H� -� 09H�

�0AH� -� 0BH�

�0CH� -� 0DH�

�0EH� -� 0FH�

�12H� -� 13H�

�14H� -� 15H�

�16H� -� 17H�

�32H� -� 33H�

�22H� -� 23H�

�24H� -� 25H�

�26H� -� 27H�

�28H� -� 29H�

�2AH� -� 2BH�

�2CH� -� 2DH�

�2EH� -� 2FH�

�30H� -� 31H�

�34H� -� 35H�

�POR� Value�

�0000H�

�0000H�

�05EEH�

�000CH�

�0000H�

�0000H�

�0000H�

�0000H�

�0000H�

�0000H�

�0000H�

�0000H�

�0000H�

�0000H�

�0000H�

�0000H�

�0000H�

�0000H�

�0000H�

�0080H�

�IPUG51_03.0,� December� 2010�

�25�

�Tri-Speed� Ethernet� MAC� User’s� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| VI-J0T-EZ-F2 | CONVERTER MOD DC/DC 6.5V 25W |

| TS-MAC-P2-UT4 | SITE LICENSE ETH MAC TRI ECP2 |

| TS-MAC-E3-UT4 | SITE LICENSE ETH MAC TRI ECP3 |

| TS-MAC-E2-UT4 | SITE LICENSE ETH MAC TRI EC/ECP |

| VI-J0T-EZ-F1 | CONVERTER MOD DC/DC 6.5V 25W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TSMACSCU2 | 功能描述:以太网模块 TriSpd Ethernet MAC RoHS:否 制造商:Lantronix 产品:Device Servers 数据速率:300 bps to 921.6 kbps, 10 Mbps, 100 Mbps 接口类型:Ethernet, Serial 工作电源电压:5 V to 15 V 工作电源电流:133 mA to 400 mA 最大工作温度:+ 70 C |

| TS-MAC-SC-U3 | 功能描述:开发软件 Ethernet MAC TriSPD RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-SC-U4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-SC-UT4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TSMACX2U2 | 功能描述:以太网模块 TriSpd Ethernet MAC RoHS:否 制造商:Lantronix 产品:Device Servers 数据速率:300 bps to 921.6 kbps, 10 Mbps, 100 Mbps 接口类型:Ethernet, Serial 工作电源电压:5 V to 15 V 工作电源电流:133 mA to 400 mA 最大工作温度:+ 70 C |

发布紧急采购,3分钟左右您将得到回复。