- 您现在的位置:买卖IC网 > PDF目录16136 > TS-MAC-XM-U4 (Lattice Semiconductor Corporation)IP CORE ETH MAC TRI-SPEED XP PDF资料下载

参数资料

| 型号: | TS-MAC-XM-U4 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 48/66页 |

| 文件大小: | 0K |

| 描述: | IP CORE ETH MAC TRI-SPEED XP |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | TSMACXMU4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页当前第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

�� �

�

Chapter� 5:�

�Application� Support�

�This� chapter� provides� application� support� information� for� the� TSMAC� IP� core.�

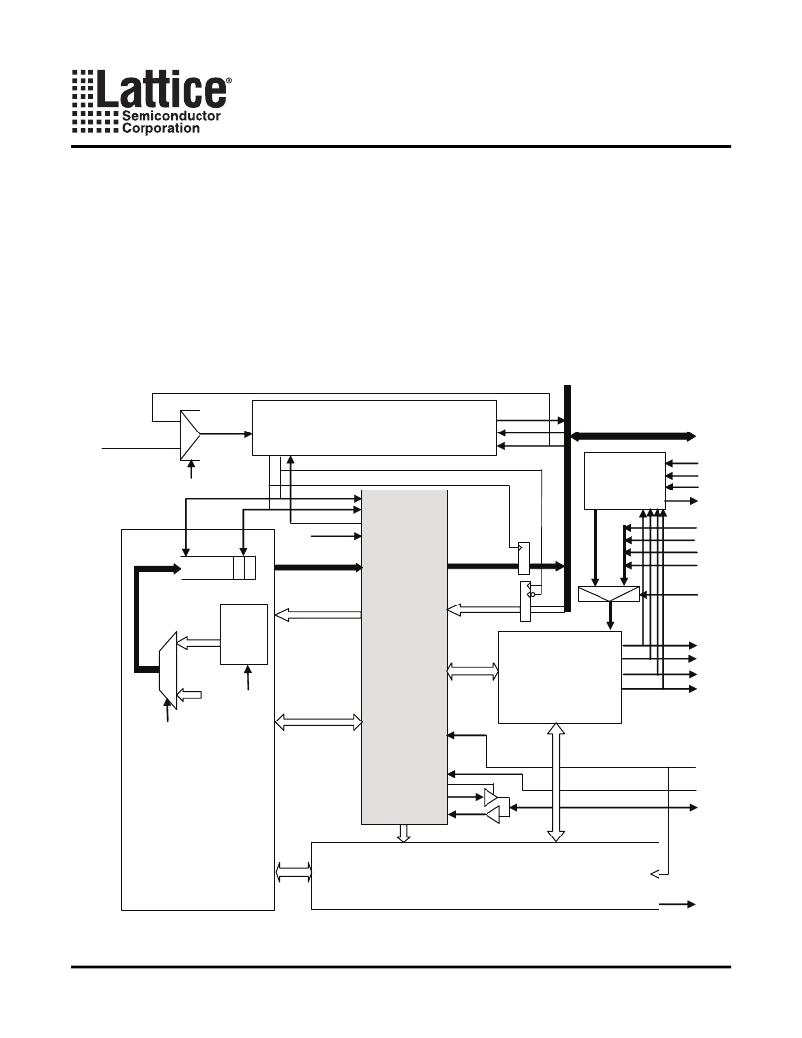

�Test� Application� Design�

�The� TSMAC� IP� core� evaluation� package� includes� a� reference� design� that� can� be� used� to� instantiate,� simulate,� map,�

�place� and� route� the� Lattice� TSMAC� IP� core� in� an� example� working� design.� This� reference� design� provides� a� loop�

�back� path� for� packets� on� the� MAC� Rx/Tx� client� interface,� through� a� FIFO� and� associated� logic.� Ethernet� packets�

�are� sourced� to� the� Rx� G/MII� and� looped� back� on� the� MAC� Rx/Tx� client� FIFO� interface.� Source� and� destination�

�addresses� in� the� ethernet� frame� can� be� swapped� so� the� looped� back� packets� on� the� Tx� G/MII� have� the� correct�

�source� and� destination� addresses.� This� design� also� provides� connections� to� the� other� interfaces� of� the� Lattice�

�TSMAC� IP� core,� including� the� SMI,� Host� Bus� and� Rx/Tx� Statistics� interfaces.� Figure� 5-1� shows� a� block� diagram� of�

�the� test� application� design.� This� loopback� design� should� be� able� to� sustain� a� 1� Gbps� throughput� with� minimum�

�sized� Ethernet� frames.�

�Figure� 5-1.� Test� Application� Design�

�ts_mac_top.v�

�sys_clk�

�TSMAC� Support� Logic�

�(buffers,� PLLs,� dividers,� muxes,� etc.)�

�gtx_clk�

�tx_clk�

�rx_clk�

�G/MII�

�TDI�

�TMS�

�Pkt_loop_clksel�

�rxmac_clk�

�JTAG�

�TCK�

�TDO�

�txmac_clk�

�FIFO�

�cpu_if_gbit_en�

�reset_n�

�clk�

�data_in�

�ready�

�Tx� Client� Intf.�

�TX� G/MII�

�reset�

�JTAG/�

�2048� x� 9�

�Rx� Client� Intf.�

�RX� G/MII�

�PAR�

�Address�

�Swap�

�Tri-�

�Speed�

�MAC�

�Core�

�Host� Bus�

�Orcastra� Bus� to�

�MAC� Host� Bus�

�and� Register�

�ack�

�error�

�retry�

�data_out�

�Add_swap�

�User� Slave�

�NULL�

�loop_enb�

�Addres� Swap�

�and� Loop� Back�

�Test� Logic�

�Misc.� Client� signals�

�Rx/Tx� Statistics�

�hclk�

�mdc�

�mdio_en�

�mdo�

�mdi�

�Interface� (USI)�

�User� Slave� Bus�

�Orcastra�

�Bus�

�SMI�

�Control�

�and� Status�

�Register� Interface� Module�

�(status/control� registers� and� statistics� counters� )�

�hclk�

�phy_reset_n�

�IPUG51_03.0,� December� 2010�

�48�

�Tri-Speed� Ethernet� MAC� User’s� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| ESM12DSES-S243 | CONN EDGECARD 24POS .156 EYELET |

| M3BFK-2040K | IDC CABLE - MSR20K/MC20F/MCF20K |

| M3BGK-2040K | IDC CABLE - MSR20K/MC20F/MCS20K |

| M3BEK-2040K | IDC CABLE - MSR20K/MC20F/MCE20K |

| TS-MAC-X2-U4 | IP CORE ETH MAC 3SPD LATTICEXP2 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TS-MAC-XM-UT4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TSMBG0505C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|100V V(BO) MAX|DO-215AA |

| TSMBG0506C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|110V V(BO) MAX|DO-214AA |

| TSMBG0507C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|145V V(BO) MAX|DO-214AA |

| TSMBG0509C | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|185V V(BO) MAX|DO-215AA |

发布紧急采购,3分钟左右您将得到回复。