- 您现在的位置:买卖IC网 > PDF目录16105 > TURBO-DECO-X2-U3 (Lattice Semiconductor Corporation)IP CORE TURBO DECODER XP2 PDF资料下载

参数资料

| 型号: | TURBO-DECO-X2-U3 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 12/22页 |

| 文件大小: | 0K |

| 描述: | IP CORE TURBO DECODER XP2 |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | TURBODECOX2U3 |

�� �

�

Lattice� Semiconductor�

�Turbo� Decoder� User’s� Guide�

�CCSDS�

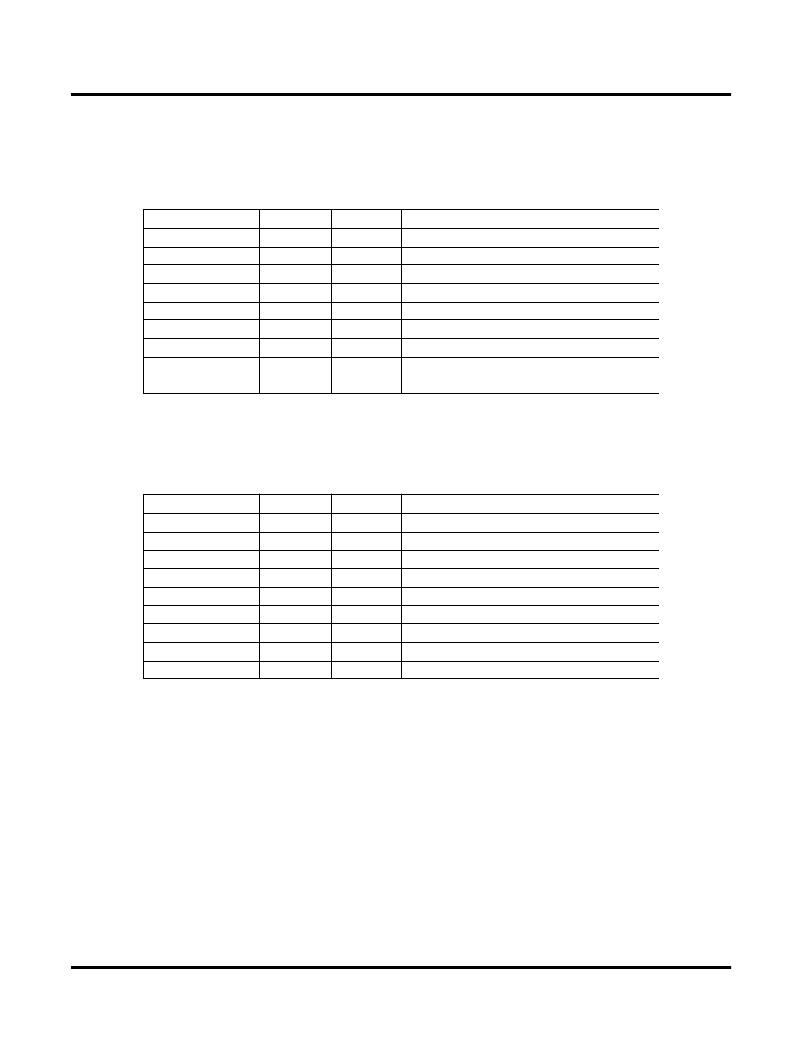

�For� CCSDS� decoder� type,� in� the� case� that� an� external� memory� is� selected;� the� following� additional� pins� are�

�required.� It� is� assumed� that� data� and� parity� are� stored� in� different� memory� buffers.� Non-interleaved� and� interleaved�

�parity� are� stored� in� different� buffers.�

�Table� 5.� Additional� I/Os� Due� to� External� Memory� for� CCSDS�

�Port� Name�

�g1_par2_odd1�

�g2_par2_odd1�

�g1_par3_odd1�

�g2_par3_odd1�

�g1_par3_even1�

�g2_par3_even1�

�wren_par3_buf1�

�wren_par4_buf1�

�wren_par5_buf1�

�I/O� Type�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Output�

�Output�

�Output�

�Width�

�3-6�

�3-6�

�3-6�

�3-6�

�3-6�

�3-6�

�1�

�1�

�1�

�Signal� Description�

�Parity� 3� (systematic)� data� port� 1�

�Parity� 3� (systematic)� data� port� 2�

�Parity� 4� (systematic)� data� port� 1�

�Parity� 4� (systematic)� data� port� 2�

�Parity� 5� (interleaved)� data� port� 1�

�Parity� 5� (interleaved)� data� port� 2�

�Write� enable� for� parity� 3� (systematic)�

�Write� enable� for� parity� 4� (systematic)�

�Write� enable� for� parity� 5� (interleaved)�

��In� the� case� where� double� buffer� is� selected� along� with� the� external� memory� the� I/O� pins� in� Table� 6� will� also� be�

�added� to� the� core� for� exchanging� data� with� the� second� buffer� in� the� case� of� CCSDS.�

�Table� 6.� Additional� I/Os� Due� to� Double� Buffering� for� CCSDS�

�Port� Name�

�g1_par2_odd2�

�g2_par2_odd2�

�g1_par3_odd2�

�g2_par3_odd2�

�g1_par3_even2�

�g2_par3_even2�

�wren_par3_buf2�

�wren_par4_buf2�

�wren_par5_buf2�

�I/O� Type�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Output�

�Output�

�Output�

�Width�

�3-6�

�3-6�

�3-6�

�3-6�

�3-6�

�3-6�

�1�

�1�

�1�

�Signal� Description�

�Parity� 3� (systematic)� data� port� 1�

�Parity� 3� (systematic)� data� port� 2�

�Parity� 4� (systematic)� data� port� 1�

�Parity� 4� (systematic)� data� port� 2�

�Parity� 5� (interleaved)� data� port� 1�

�Parity� 5� (interleaved)� data� port� 2�

�Write� enable� for� parity� 3� (systematic)�

�Write� enable� for� parity� 4� (systematic)�

�Write� enable� for� parity� 5� (interleaved)�

��12�

�相关PDF资料 |

PDF描述 |

|---|---|

| TURBO-DECO-SC-U3 | IP CORE TURBO DECODER SC/SCM |

| MAX6315US29D3+T | IC RESET CIRCUIT 2.93V SOT143-4 |

| DC630R-102M | POWER CHOKE HIGH CURRENT 1.0 UH |

| M3AKK-3436J | IDC CABLE - MSC34K/MC34G/MPK34K |

| 1485E9P | WIREWAY 90 DEG INSIDE OPENG 8X8" |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TURBO-DECO-X2-UT3 | 功能描述:开发软件 TURBO DECODER RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TURBO-DECO-XM-U3 | 功能描述:开发软件 Turbo Decoder RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TURBO-DECO-XM-UT3 | 功能描述:开发软件 TURBO DECODER RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TURBO-DECO-XP-N1 | 功能描述:编码器、解码器、复用器和解复用器 Turbo Decoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

| TURBO-ENCO-E2-U3 | 功能描述:编码器、解码器、复用器和解复用器 Turbo Encoder RoHS:否 制造商:Micrel 产品:Multiplexers 逻辑系列:CMOS 位数: 线路数量(输入/输出):2 / 12 传播延迟时间:350 ps, 400 ps 电源电压-最大:2.625 V, 3.6 V 电源电压-最小:2.375 V, 3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-44 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。