- 您现在的位置:买卖IC网 > PDF目录225474 > UT54ACS191-PVAR AC SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, CDIP16 PDF资料下载

参数资料

| 型号: | UT54ACS191-PVAR |

| 元件分类: | 计数器 |

| 英文描述: | AC SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, CDIP16 |

| 封装: | DIP-16 |

| 文件页数: | 1/6页 |

| 文件大小: | 58K |

| 代理商: | UT54ACS191-PVAR |

123

Rad-Hard MSI Logic

UT54ACS191/UT54ACTS191

Radiation-Hardened

Synchronous 4-Bit Up-Down Binary Counters

FEATURES

Single down/up count control line

counters

Fully synchronous in count modes

Asynchronously presetable with load control

radiation-hardened CMOS

High speed

Low power consumption

Single 5 volt supply

Available QML Q or V processes

Flexible package

- 16-pin DIP

- 16-lead flatpack

DESCRIPTION

The UT54ACS191 and the UT54ACTS191 are synchronous 4-

bit reversible up-down binary counters. Synchronous counting

operation is provided by having all flip-flops clocked simulta-

neously so that the outputs change coincident with each other

when so instructed. Synchronous operation eliminates the out-

put counting spikes associated with asynchronous counters.

The outputs of the four flip-flops are triggered on a low-to-high-

level transition of the clock input if the enable input (CTEN) is

low. A logic one applied to CTEN inhibits counting. The di-

rection of the count is determined by the level of the down/up

(D/U) input. When D/U is low, the counter counts up and when

D/U is high, it counts down.

The counters feature a fully independent clock circuit. Changes

at control inputs (CTEN and D/U) that will modify the operating

mode have no effect on the contents of the counter until clocking

occurs.

The counters are fully programmable. The outputs may be

preset to either logic level by placing a low on the load input

and entering the desired data at the data inputs. The output will

change to agree with the data inputs independently of the level

of the clock input. The asynchronous load allows counters to

be used as modulo-N dividers by simply modifying the count

length with the preset inputs.

Two outputs have been made available to perform the cascading

function: ripple clock and maximum/minimum (MAX/MIN)

count. The MAX/MIN output produces a high-level output

pulse with a duration approximately equal to one complete cycle

of the clock while the count is zero (all outputs low) counting

down or maximum (15) counting up.

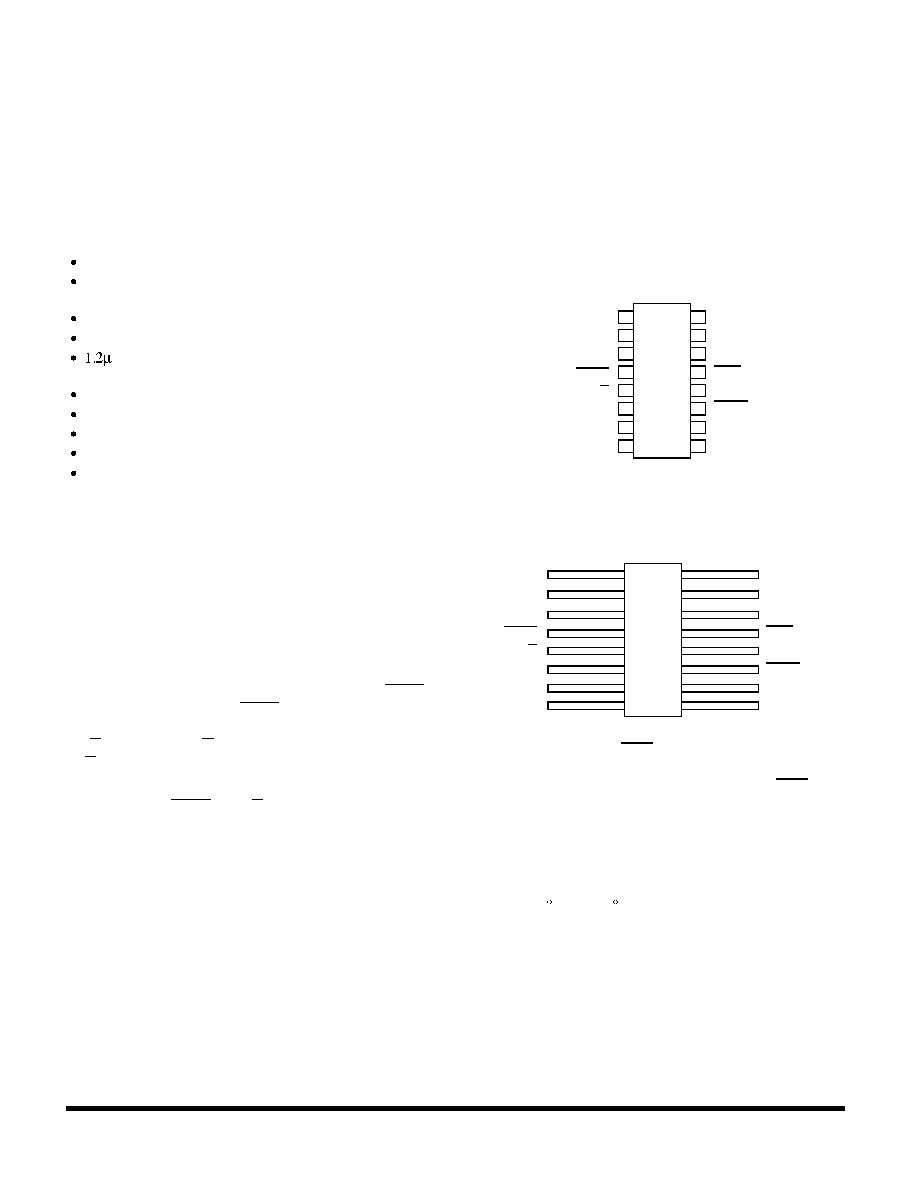

PINOUTS

16-Pin DIP

Top View

16-Lead Flatpack

Top View

The ripple clock output (RCO) produces a low-level output

pulse under those same conditions but only while the clock input

is low. The counters easily cascade by feeding the RCO to the

enable input of the succeeding counter if parallel clocking is

used, or to the clock input if parallel enabling is used. Use the

MAX/MIN count output to accomplish look-ahead for high-

speed operation.

The devices are characterized over full military temperature

range of -55 C to +125

1

3

5

6

15

13

10

B

A

D/

Q

V

A

RCO

C

9

SS

LOAD

2

4

7

16

14

12

11

DD

9

Q

CTEN

U

C

D

CLK

MAX/MIN

C

SS

相关PDF资料 |

PDF描述 |

|---|---|

| UT54ACS191-PQXR | AC SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, CDIP16 |

| UT54ACS191-PQCH | AC SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, CDIP16 |

| UT54ACS191-PQAH | AC SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, CDIP16 |

| UT54ACS191-UCX | AC SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, CDFP16 |

| UT54ACS191-UCC | AC SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, CDFP16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| UT54ACS191-PVCH | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Synchronous Up/Down Counter |

| UT54ACS191-PVCR | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Synchronous Up/Down Counter |

| UT54ACS191-PVXH | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Synchronous Up/Down Counter |

| UT54ACS191-PVXR | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Synchronous Up/Down Counter |

| UT54ACS191-UQAH | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Synchronous Up/Down Counter |

发布紧急采购,3分钟左右您将得到回复。