- 您现在的位置:买卖IC网 > PDF目录202171 > V54C3128804VCLC7E (PROMOS TECHNOLOGIES INC) 16M X 8 SYNCHRONOUS DRAM, 7 ns, PBGA54 PDF资料下载

参数资料

| 型号: | V54C3128804VCLC7E |

| 厂商: | PROMOS TECHNOLOGIES INC |

| 元件分类: | DRAM |

| 英文描述: | 16M X 8 SYNCHRONOUS DRAM, 7 ns, PBGA54 |

| 封装: | FBGA-54 |

| 文件页数: | 10/56页 |

| 文件大小: | 681K |

| 代理商: | V54C3128804VCLC7E |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

18

V54C3128(16/80/40)4VC Rev. 1.1 October 2007

ProMOS TECHNOLOGIES

V54C3128(16/80/40)4VC

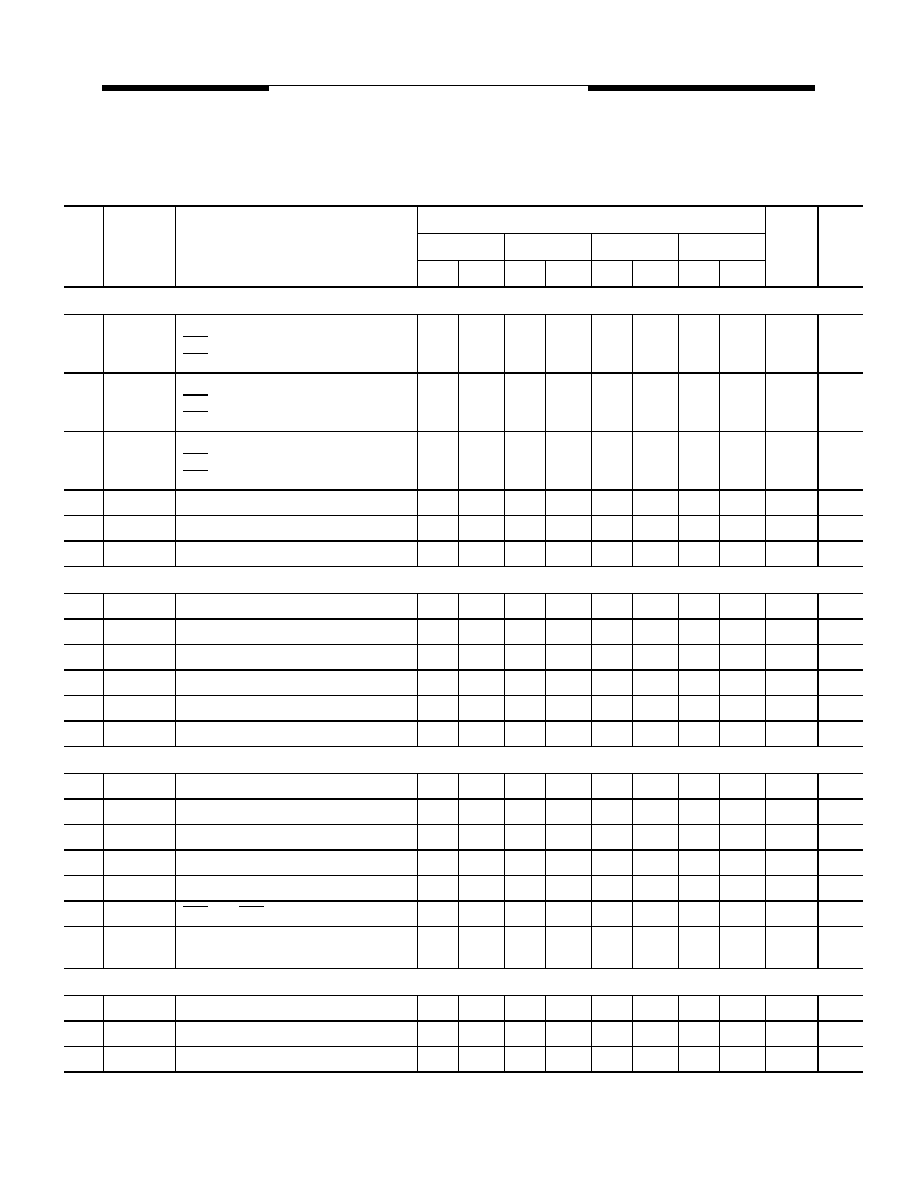

AC Characteristics 1,2, 3

TA = 0 to 70 °C (Commercial), -40 to 85°C (Industrial); -40 to 125°C (Extended), VSS = 0 V; VDD = 3.3 V ± 0.3 V, tT =

1 ns

#

Symbol

Parameter

Limit Values

Unit

Note

-5

-6

-7PC

-7

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Clock and Clock Enable

1tCK

Clock Cycle Time

CAS Latency = 3

CAS Latency = 2

5

–

6

–

7

7.5

–

7

7.5

–

s

ns

2fCK

Clock Frequency

CAS Latency = 3

CAS Latency = 2

200

–

166

–

143

133

–

143

133

–

MHz

3tAC

Access Time from Clock

CAS Latency = 3

CAS Latency = 2

–

_

4.5

–

_

5.4

–

_

5.4

–

_

5.4

6

ns

2, 4

4tCH

Clock High Pulse Width

2

–

2.5

–

2.5

–

2.5

–

ns

5tCL

Clock Low Pulse Width

2

–

2.5

–

2.5

–

2.5

–

ns

6tT

Transition Tim

0.3

1.2

0.3

1.2

0.3

1.2

0.3

1.2

ns

Setup and Hold Times

7tIS

Input Setup Time

1.5

–

1.5

–

1.5

–

1.5

–

ns

5

8tIH

Input Hold Time

1

–

1

–

0.8

–

0.8

–

ns

5

9tMRD

Mode Register Set to Command delay

2

–

2

–

2

–

2

–

CLK

10

tSB

Power Down Mode Entry Time

0

5

0

6

0

7

0

7

ns

11

tDS

Data-in setup time

1.5–1.5

–1.5–1.5

–

ns

12

tDH

Data-in hold time

1

–

1

–

0.8

–

0.8

–

ns

Common Parameters

13

tRCD

Row to Column Delay Time

15

–

15

–

15

–

15

–

ns

6

14

tRP

Row Precharge Time

15

–

15

–

15

–

15

–

ns

6

15

tRAS

Row Active Time

40

100K

42

100K

42

100K

42

100K

ns

6

16

tRC

Row Cycle Time

55

–60–65–

65

–

ns

6

17

tRRD

Activate(a) to Activate(b) Command Period

12

–

12

–

14

–

14

–

ns

6

18

tCCD

CAS(a) to CAS(b) Command Period

1

–

1

–

1

–

1

–

CLK

19

tDPL

Data-in to Precharge Command for Manual

precharge

2–

2–2

–2–

CLK

Refresh Cycle

20

tRFC

Row Refresh Cycle Time

55

—

60

—

60

—

70

—

ns

6

21

tREF

Refresh Period (4096 cycles)

—

64

—

64

—

64

—

64

ms

22

tSREX

Self Refresh Exit Time

1

—

1

—

1

—

1

—

CLK

相关PDF资料 |

PDF描述 |

|---|---|

| V54C3128804VCT7PCE | 16M X 8 SYNCHRONOUS DRAM, 7 ns, PDSO54 |

| V54C316162VAT10 | 1M X 16 SYNCHRONOUS DRAM, 8 ns, PDSO50 |

| V54C3256164VAT6 | 16M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| V54C3256404VDS8IPC | 64M X 4 SYNCHRONOUS DRAM, 6 ns, PBGA60 |

| V54C3256404VDUG7 | 64M X 4 SYNCHRONOUS DRAM, 5.4 ns, PBGA54 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| V54C3128804VS | 制造商:MOSEL 制造商全称:MOSEL 功能描述:128Mbit SDRAM 3.3 VOLT, TSOP II / SOC PACKAGE 8M X 16, 16M X 8, 32M X 4 |

| V54C3128804VT | 制造商:MOSEL 制造商全称:MOSEL 功能描述:128Mbit SDRAM 3.3 VOLT, TSOP II / SOC PACKAGE 8M X 16, 16M X 8, 32M X 4 |

| V54C316162 | 制造商:MOSEL 制造商全称:MOSEL 功能描述:200/183/166/143 MHz 3.3 VOLT, 4K REFRESH ULTRA HIGH PERFORMANCE 1M X 16 SDRAM 2 BANKS X 512Kbit X 16 |

| V54C316162V | 制造商:MOSEL 制造商全称:MOSEL 功能描述:200/183/166/143 MHz 3.3 VOLT, 4K REFRESH ULTRA HIGH PERFORMANCE 1M X 16 SDRAM 2 BANKS X 512Kbit X 16 |

| V54C316162V-5 | 制造商:MOSEL 制造商全称:MOSEL 功能描述:200/183/166/143 MHz 3.3 VOLT, 4K REFRESH ULTRA HIGH PERFORMANCE 1M X 16 SDRAM 2 BANKS X 512Kbit X 16 |

发布紧急采购,3分钟左右您将得到回复。