- 您现在的位置:买卖IC网 > PDF目录361766 > W152-11X Eight Distributed-Output Clock Driver PDF资料下载

参数资料

| 型号: | W152-11X |

| 英文描述: | Eight Distributed-Output Clock Driver |

| 中文描述: | 八分布式输出时钟驱动器 |

| 文件页数: | 2/8页 |

| 文件大小: | 142K |

| 代理商: | W152-11X |

W152

Document #: 38-07148 Rev. **

Page 2 of 8

Overview

The W152 products are eight-output zero delay buffers. A

Phase-Locked Loop (PLL) is used to take a time-varying signal

and provide eight copies of that same signal out. The external

feedback to the PLL provides outputs in phase with the refer-

ence inputs.

Internal dividers exist in some options allowing the user to get

a simple multiple (/2, x2, x4) of the reference input, for details

see

Table 1

. Because the outputs are separated into two

banks, it is possible to provide some combination of these mul-

tiples at the same time.

Spread Aware

Many systems being designed now utilize a technology called

Spread Spectrum Frequency Timing Generation. Cypress has

been one of the pioneers of SSFTG development, and we de-

signed this product so as not to filter off the Spread Spectrum

feature of the Reference input, assuming it exists. When a

zero delay buffer is not designed to pass the SS feature

through, the result is a significant amount of tracking skew

which may cause problems in systems requiring synchroniza-

tion.

For more details on Spread Spectrum timing technology,

please see the Cypress application note titled,

“

EMI Suppres-

sion Techniques with Spread Spectrum Frequency Timing

Generator (SSFTG) ICs.

”

Functional Description

Logic inputs provide the user the ability to turn off one or both

banks of clocks when not in use, as described in

Table 2

. Dis-

abling a bank of unused outputs will reduce jitter and power

consumption, and will also reduce the amount of EMI gener-

ated by the W152.

These same inputs allow the user to bypass the PLL entirely

if so desired. When this is done, the device no longer acts as

a zero delay buffer, it simply reverts to a standard eight-output

clock driver.

The W152 PLL enters an auto power-down mode when there

are no rising edges on the REF input. In this mode, all outputs

are three-stated and the PLL is turned off.

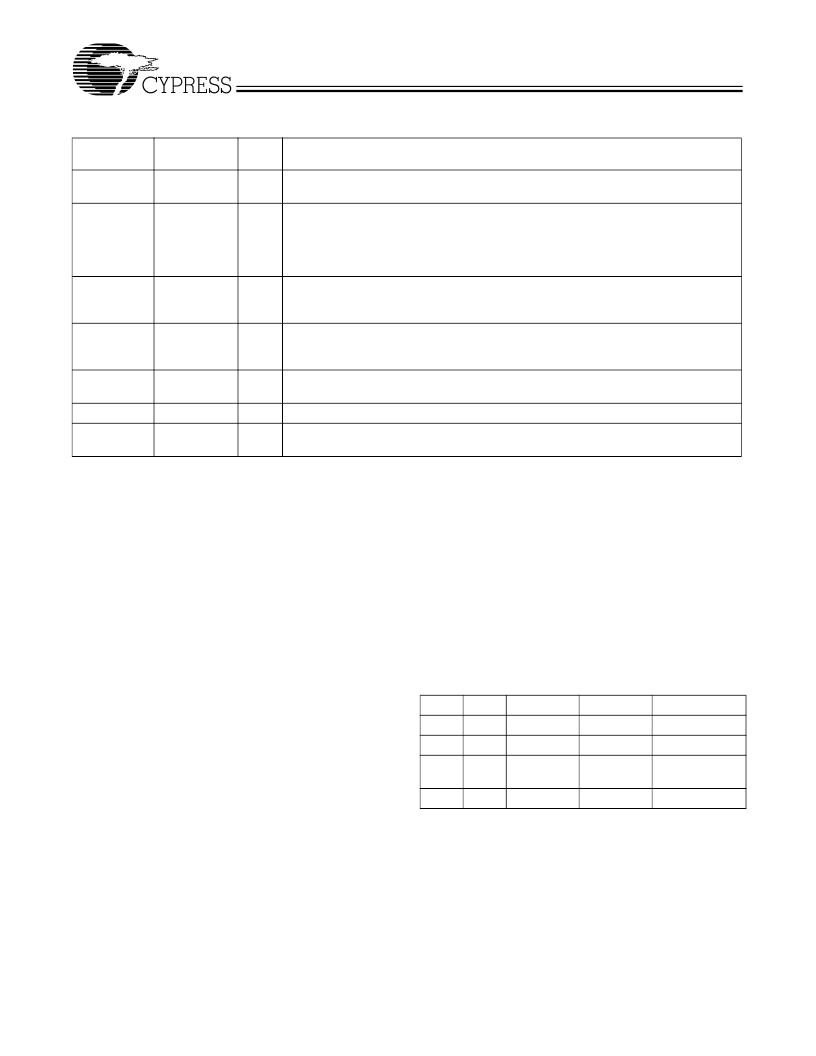

Pin Definitions

Pin Name

REF

Pin No.

1

Pin

Type

I

Pin Description

Reference Input:

The output signals QA0:3 through QB0:3 will be synchronized to

this signal unless the device is programmed to bypass the PLL.

Feedback Input:

When programmed to zero delay buffer mode, this input must be

fed by one of the outputs (QA0:3 or QB0:3) to ensure proper functionality. If the trace

between FBIN and the output pin being used for feedback is equal in length to the

traces between the outputs and the signal destinations, then the signals received at

the destinations will be synchronized to the REF signal input.

Outputs from Bank A:

The frequency of the signals provided by these pins is deter-

mined by the feedback signal connected to FBIN, and the specific W152 option being

used. See

Table 2

.

Outputs from Bank B:

The frequency of the signals provided by these pins is deter-

mined by the feedback signal connected to FBIN, and the specific W152 option being

used. See

Table 2

.

Power Connections:

Connect to 3.3V. Use ferrite beads to help reduce noise for

optimal jitter performance.

Ground Connections:

Connect all grounds to the common system ground plane.

Function Select Inputs:

Tie to V

DD

(HIGH, 1) or GND (LOW, 0) as desired per

Table 2

.

FBIN

16

I

QA0:3

2, 3, 14, 15

O

QB0:3

6, 7, 10, 11

O

VDD

4, 13

P

GND

SEL0:1

5, 12

9, 8

G

I

Table 2. Input Logic

SEL1

0

0

1

SEL0

0

1

0

QA0:3

Three-State Three-State

Active

Active

QB0:3

PLL

Shutdown

Active, Utilized

Shutdown,

Bypassed

Active, Utilized

Three-State

Active

1

1

Active

Active

相关PDF资料 |

PDF描述 |

|---|---|

| W152-12G | EIGHT DISTRIBUTED-OUTPUT CLOCK DRIVER|CMOS|SOP|16PIN|PLASTIC |

| W152-11G | EIGHT DISTRIBUTED-OUTPUT CLOCK DRIVER|CMOS|SOP|16PIN|PLASTIC |

| W155G | CPU System Clock Generator |

| W156 | Clocks and Buffers |

| W158H | CPU System Clock Generator |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W152-11XT | 制造商:Cypress Semiconductor 功能描述:Zero Delay PLL Clock Buffer Single 15MHz to 140MHz 16-Pin TSSOP T/R |

| W152-12G | 功能描述:锁相环 - PLL REMARK TO CY23S08 COM RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| W152-12GT | 功能描述:锁相环 - PLL REMARK TO CY23S08 COM RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| W152-12X | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Eight Distributed-Output Clock Driver |

| W152-1G | 制造商:Cypress Semiconductor 功能描述:Zero Delay PLL Clock Buffer Single 15MHz to 140MHz 16-Pin SOIC 制造商:Rochester Electronics LLC 功能描述:ZERO DELAY BUFFER - Bulk |

发布紧急采购,3分钟左右您将得到回复。