- 您现在的位置:买卖IC网 > PDF目录276857 > W1D64M72R8A-3.75AR-QB1 (XILINX INC) 64M X 8 DDR DRAM MODULE, 0.5 ns, DMA240 PDF资料下载

参数资料

| 型号: | W1D64M72R8A-3.75AR-QB1 |

| 厂商: | XILINX INC |

| 元件分类: | DRAM |

| 英文描述: | 64M X 8 DDR DRAM MODULE, 0.5 ns, DMA240 |

| 封装: | MO-237, DIMM-240 |

| 文件页数: | 9/11页 |

| 文件大小: | 255K |

| 代理商: | W1D64M72R8A-3.75AR-QB1 |

DDR2-400, 533

Single Rank, x8 Registered SDRAM DIMMs

DDR2_RDIMM_1 rank_x8_spec

Rev. 1.0 - December, 04

Wintec Industries, Inc., reserves the right to change datasheets and/or products without any notice.

2004 Wintec Industries, Inc.

7

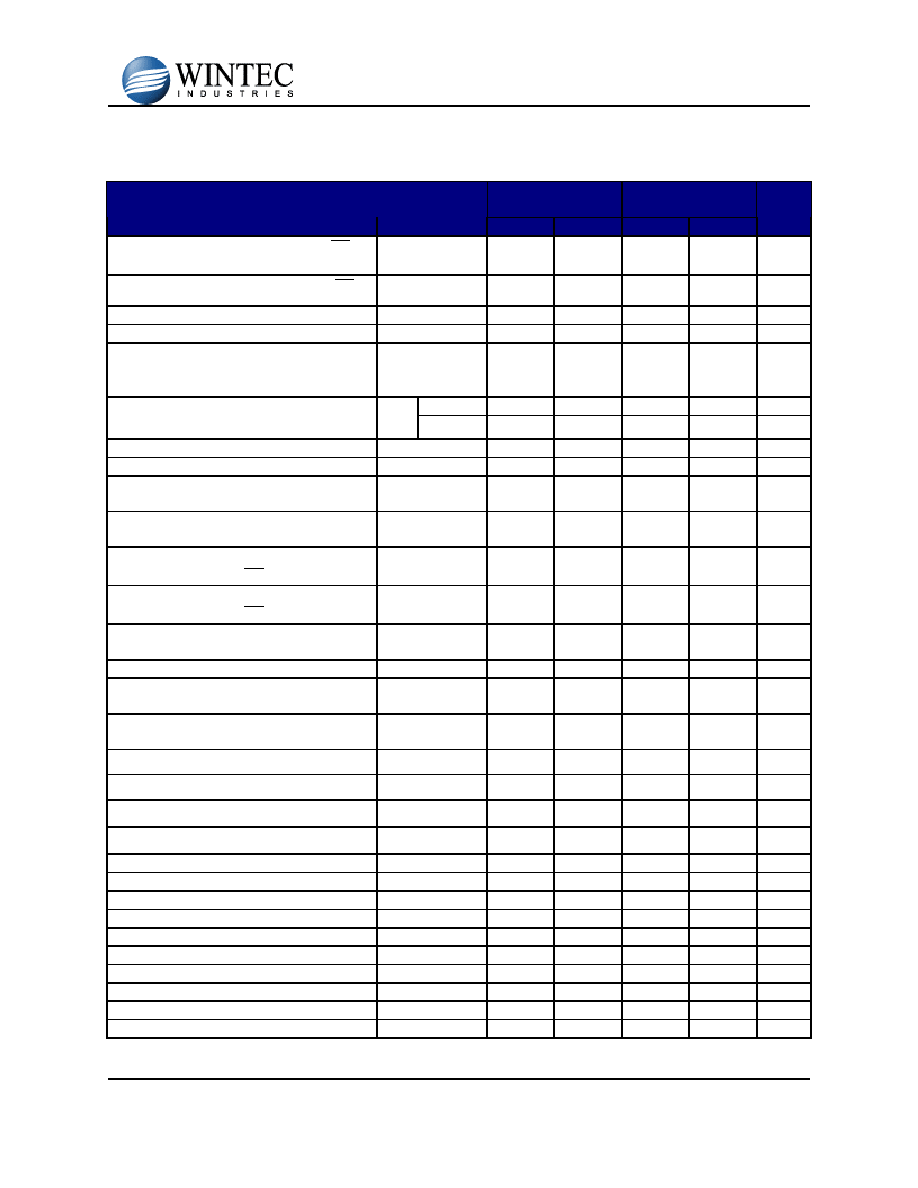

Electrical Characteristics and AC Timings:

VDD = +1.8V ± 0.1V, VDDQ = +1.8V ± 0.1V, VREF = VSS, f =100MHz, 0°C<TOPR <+55°C, VOUT(DC) = VDDQ/2

-5

DDR2-400

-3.75

DDR2-533

Parameter

Symbol

MIN

MAX

MIN

MAX

Units

DQ output access time from CK/ CK

tAC

-600

+600

-500

+500

ps

DQS output access time from CK/ CK

tDQSCK

-500

+500

-450

+450

ps

CK high-level width

tCH

0.45

0.55

0.45

0.55

tCK

CK low-level width

tCL

0.45

0.55

0.45

0.55

tCK

CK half period

tHP

MIN

(tCH,

tCL)

-

MIN

(tCH,

tCL)

-

ps

CL=3

5,000

8,000

5,000

8,000

ps

Clock cycle time

tCK

CL=4 & 5

5,000

8,000

3,750

8,000

ps

DQ and DM input hold time

tDH

400

-

350

-

ps

DQ and DM input setup time

tDS

400

-

350

-

ps

Control & Address input pulse width for

each input

tIPW

0.6

-

0.6

-

tCK

DQ and DM input pulse width for each

input

tDIPW

0.35

-

0.35

-

tCK

Data-out high-impedance time from

CK/ CK

tHZ

-

tACmax

-

tACmax

ps

Data-out low-impedance time from

CK/ CK

tLZ

tACmin

tACmax

tACmin

tACmax

ps

DQS-DQ skew for DQS and associated DQ

signals

tDQSQ

-

350

-

300

ps

Data hold skew factor

tQHS

-

450

-

400

ps

Data output hold time from DQS

tQH

tHP-

tQHS

-

tHP-

tQHS

-

ps

Write command to 1st DQS latching

transition

tDQSS

WL-0.25

WL+

0.25

WL-0.25

WL+

0.25

tCK

DQS input low/high pulse width

tDQSL/H

0.35

-

0.35

-

tCK

DQS falling edge to CK setup time

tDSS

0.2

-

0.2

-

tCK

DQS falling edge hold time from CK

tDSH

0.2

-

0.2

-

tCK

Mode register set command cycle time

tMRD

2

-

2

-

tCK

Write preamble setup time

tWPRES

0

-

0

-

ps

Write preamble

tWPRE

0.25

-

0.25

-

tCK

Write postamble

tWPST

0.40

0.60

0.40

0.60

tCK

Read preamble

tRPRE

0.9

1.1

0.9

1.1

tCK

Read postamble

tRPST

0.4

0.6

0.4

0.6

tCK

Active to Precharge command

tRAS

45

70,000

45

70,000 ns

Active to Active command period

tRC

60

-

60

-

ns

Refresh to Refresh command interval

tRFC

105

-

105

-

ns

Active to Read/Write delay

tRCD

15

-

15

-

ns

Precharge command period

tRP

15

-

15

-

ns

相关PDF资料 |

PDF描述 |

|---|---|

| W1D64M72R8A-5AE-PA | 64M X 8 DDR DRAM MODULE, 0.5 ns, DMA240 |

| W1D64M72R8A-5AR-JA | 64M X 8 DDR DRAM MODULE, 0.5 ns, DMA240 |

| W1D64M72R8B-5AE-FA1 | 64M X 8 DDR DRAM MODULE, 0.5 ns, DMA240 |

| W1D64M72R8B-5AE-QA1 | 64M X 8 DDR DRAM MODULE, 0.5 ns, DMA240 |

| W9816G6IH-5 | 1M X 16 SYNCHRONOUS DRAM, 4.5 ns, PDSO50 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W1D-ANPHY | 制造商:EVERLIGHT 制造商全称:Everlight Electronics Co., Ltd 功能描述:White Chip LED With Right Angle Lens |

| W1D-ANPHY-3T | 制造商:EVERLIGHT 制造商全称:Everlight Electronics Co., Ltd 功能描述:White Chip LED |

| W1D-ANQHY | 制造商:EVERLIGHT 制造商全称:Everlight Electronics Co., Ltd 功能描述:Reverse Package Chip LED |

| W1D-APQHY | 制造商:EVERLIGHT 制造商全称:Everlight Electronics Co., Ltd 功能描述:Chip LED (1.1mm Height) |

| W1D-DP1Q2QY | 制造商:EVERLIGHT 制造商全称:Everlight Electronics Co., Ltd 功能描述:Chip LED (0.4mm Height) |

发布紧急采购,3分钟左右您将得到回复。