- 您现在的位置:买卖IC网 > PDF目录276894 > W3EG6433S335JD3 (MICROSEMI CORP-PMG MICROELECTRONICS) 32M X 64 DDR DRAM MODULE, 0.7 ns, DMA184 PDF资料下载

参数资料

| 型号: | W3EG6433S335JD3 |

| 厂商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分类: | DRAM |

| 英文描述: | 32M X 64 DDR DRAM MODULE, 0.7 ns, DMA184 |

| 封装: | DIMM-184 |

| 文件页数: | 9/12页 |

| 文件大小: | 262K |

| 代理商: | W3EG6433S335JD3 |

6

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

W3EG6433S-D3

-JD3

November 2005

Rev. 2

PRELIMINARY

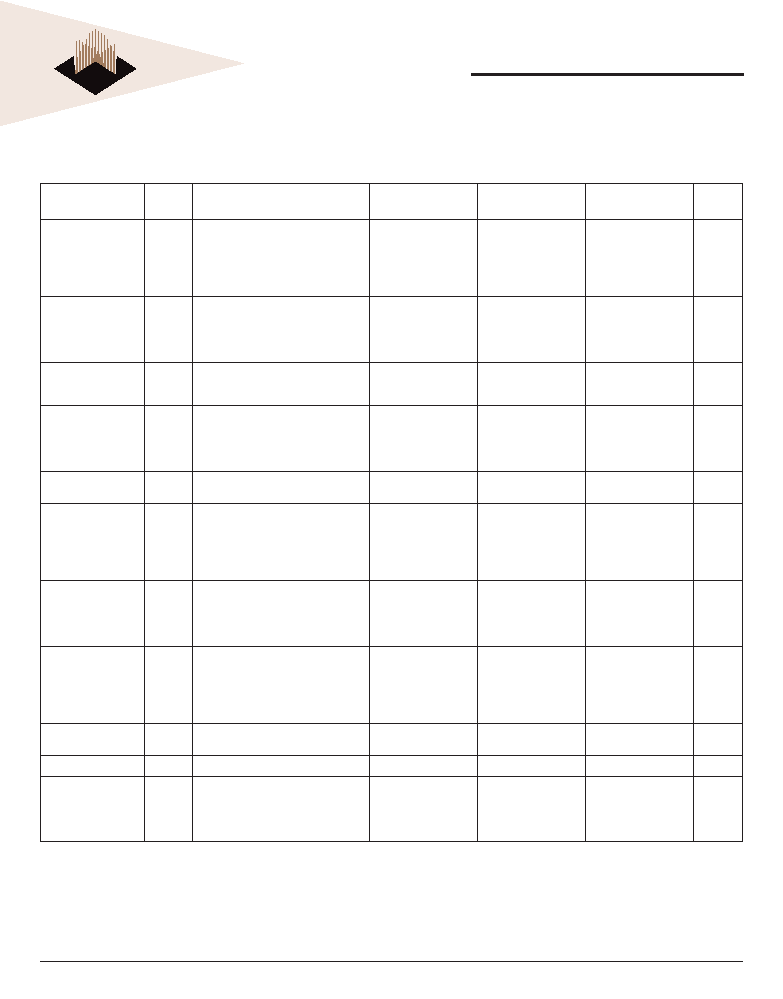

IDD SPECIFICATIONS AND TEST CONDITIONS

0°C TA 70°C, VCCQ = 2.5V ± 0.2V, VCC = 2.5V ± 0.2V

Includes DDR SDRAM component only

Parameter

Symbol Conditions

DDR333@CL=2.5

Max

DDR266@CL=2

Max

DDR266@CL=2/2.5

Max

Units

Operating Current

IDD0

One device bank; Active - Precharge;

tRC=tRC (MIN); tCK=tCK (MIN); DQ,DM

and DQS inputs changing once per

clock cycle; Address and control

inputs changing once every two

cycles.

680

640

mA

Operating Current

IDD1

One device bank; Active-Read-

Precharge Burst = 2; tRC=tRC (MIN);

tCK=tCK (MIN); lOUT = 0mA; Address

and control inputs changing once per

clock cycle.

880

800

mA

Precharge Power-

Down Standby

Current

IDD2P

All device banks idle; Power-down

mode; tCK=tCK (MIN); CKE=(low)

24

rnA

Idle Standby Current

IDD2F

CS# = High; All device banks idle;

tCK=tCK (MIN); CKE = high; Address

and other control inputs changing

once per clock cycle. VIN = VREF for

DQ, DQS and DM.

200

180

mA

Active Power-Down

Standby Current

IDD3P

One device bank active; Power-Down

mode; tCK (MIN); CKE=(low)

240

200

mA

Active Standby

Current

IDD3N

CS# = High; CKE = High; One device

bank; Active-Precharge; tRC=tRAS

(MAX); tCK=tCK (MIN); DQ, DM and

DQS inputs changing twice per clock

cycle; Address and other control

inputs changing once per clock cycle.

360

320

mA

Operating Current

IDD4R

Burst = 2; Reads; Continuous burst;

One device bank active; Address

and control inputs changing once

per clock cycle; TCK= TCK (MIN); lOUT

= 0mA.

1,120

960

mA

Operating Current

IDD4W

Burst = 2; Writes; Continuous burst;

One device bank active; Address

and control inputs changing once per

clock cycle; tCK=tCK (MIN); DQ,DM

and DQS inputs changing once per

clock cycle.

1,160

1,000

rnA

Auto Refresh

Current

IDD5

tRC = tRC (MIN)

1,320

1,240

mA

Self Refresh Current

IDD6

CKE 0.2V

16

mA

Operating Current

IDD7A

Four bank interleaving Reads (BL=4)

with auto precharge with tRC=tRC

(MIN); tCK=tCK (MIN); Address and

control inputs change only during

Active Read or Write commands.

2,400

2,000

mA

NOTES:

Module IDD was calculated on the basis of component IDD and can be different measured according to dq hearing cap.

IDD specication is based on

SAMSUNG components. Other DRAM manufactures specication may be different.

相关PDF资料 |

PDF描述 |

|---|---|

| W3EG72125S265D3SG | 128M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| W3EG72128S262JD3M | 128M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| W3EG72128S265D3MG | 128M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| W3EG72128S335JD3SG | 128M X 72 DDR DRAM MODULE, 0.7 ns, DMA184 |

| W3HG2128M72AER665AD6MG | 256M X 72 DDR DRAM MODULE, 0.45 ns, DMA240 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W3EG6433S-AD4 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:256MB - 32Mx64 DDR SDRAM UNBUFFERED, w/PLL |

| W3EG6433S-BD4 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:256MB - 32Mx64 DDR SDRAM UNBUFFERED, w/PLL |

| W3EG6433S-D3 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:256MB - 2x16Mx64 DDR SDRAM UNBUFFERED |

| W3EG6433S-JD3 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:256MB - 2x16Mx64 DDR SDRAM UNBUFFERED |

| W3EG6462S202D3 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512MB - 2x32Mx64 DDR SDRAM UNBUFFERED |

发布紧急采购,3分钟左右您将得到回复。