- 您现在的位置:买卖IC网 > PDF目录276891 > W3EG6437S202D4MG (WHITE ELECTRONIC DESIGNS CORP) 32M X 64 DDR DRAM MODULE, 0.75 ns, DMA200 PDF资料下载

参数资料

| 型号: | W3EG6437S202D4MG |

| 厂商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分类: | DRAM |

| 英文描述: | 32M X 64 DDR DRAM MODULE, 0.75 ns, DMA200 |

| 封装: | ROHS COMPLIANT, SO-DIMM-200 |

| 文件页数: | 8/12页 |

| 文件大小: | 300K |

| 代理商: | W3EG6437S202D4MG |

5

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

White Electronic Designs

May 2005

Rev. 1

White Electronic Designs Corp. reserves the right to change products or specications without notice.

PRELIMINARY*

W3EG6437S-D4

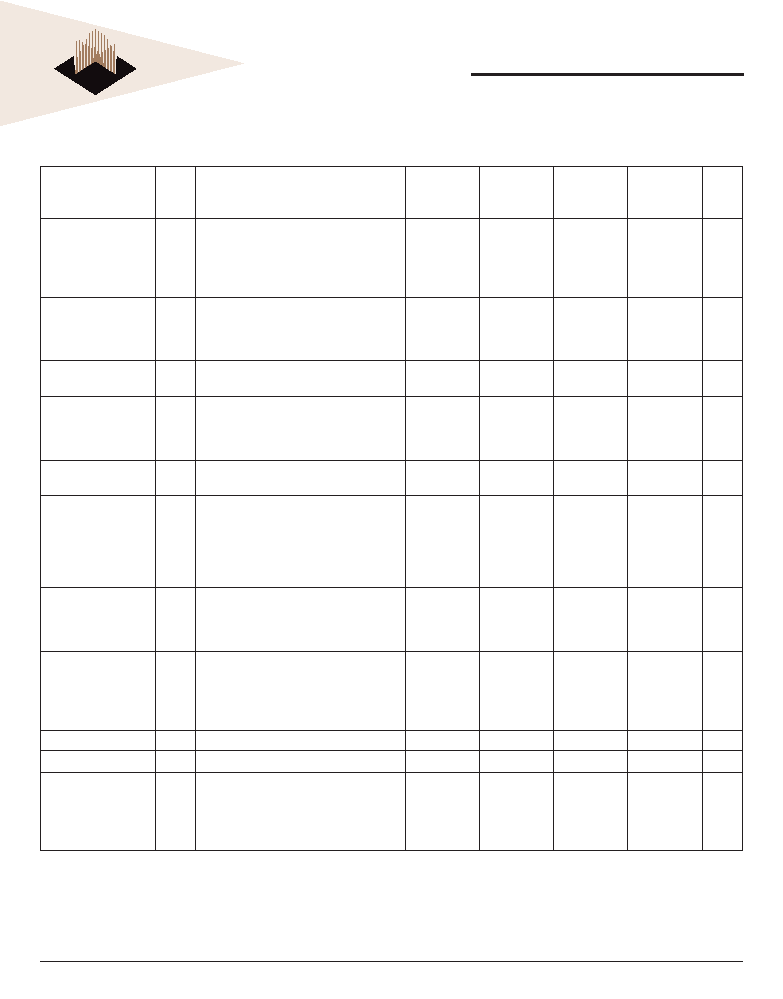

IDD SPECIFICATIONS AND TEST CONDITIONS

0°C ≤ TA ≤ 70°C, VCCQ = 2.5V ±0.2V, VCC = 2.5V ±0.2V

Parameter

Symbol Conditions

DDR403

@CL=3

Max

DDR333

@CL=2.5

Max

DDR266

@CL=2, 2.5

Max

DDR200

@CL=2

Max

Units

Operating Current

IDD0

One device bank; Active - Precharge;

tRC=tRC(MIN); tCK=tCK(MIN); DQ,DM and

DQS inputs changing once per clock cycle;

Address and control inputs changing once

every two cycles.

1100

980

900

mA

Operating Current

IDD1

One device bank; Active-Read-Precharge;

Burst = 2; tRC=tRC(MIN);tCK=tCK(MIN); Iout =

0mA; Address and control inputs changing

once per clock cycle.

1300

1200

1080

mA

Precharge Power-

Down Standby Current

IDD2P

All device banks idle; Power- down mode;

tCK=tCK(MIN); CKE=(low)

32

mA

Idle Standby Current

IDD2F

CS# = High; All device banks idle;

tCK=tCK(MIN); CKE = high; Address and other

control inputs changing once per clock cycle.

Vin = Vref for DQ, DQS and DM.

480

400

360

mA

Active Power-Down

Standby Current

IDD3P

One device bank active; Power-down mode;

tCK(MIN); CKE=(low)

320

240

200

mA

Active Standby Current

IDD3N

CS# = High; CKE = High; One device

bank; Active-Precharge; tRC=tRAS(MAX);

tCK=tCK(MIN); DQ, DM and DQS inputs

changing twice per clock cycle; Address and

other control inputs changing once per clock

cycle.

560

480

400

mA

Operating Current

IDD4R

Burst = 2; Reads; Continous burst; One

device bank active;Address and control

inputs changing once per clock cycle;

tCK=tCK(MIN); Iout = 0mA.

1600

1360

1140

mA

Operating Current

IDD4W

Burst = 2; Writes; Continous burst; One

device bank active; Address and control

inputs changing once per clock cycle;

tCK=tCK(MIN); DQ,DM and DQS inputs

changing twice per clock cycle.

1420

1260

1040

mA

Auto Refresh Current

IDD5

tRC=tRC(MIN)

1600

1500

1340

mA

Self Refresh Current

IDD6

CKE

≤ 0.2V

32

mA

Operating Current

IDD7A

Four bank interleaving Reads (BL=4)

with auto precharge with tRC=tRC (MIN);

tCK=tCK(MIN); Address and control inputs

change only during Active Read or Write

commands.

2600

2240

1920

mA

相关PDF资料 |

PDF描述 |

|---|---|

| W3EG72128S202BD4-M | 128M X 72 DDR DRAM MODULE, 0.75 ns, DMA200 |

| W3EG7262S262D3MG | 64M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| W3HG264M72EER806PD4MG | 128M X 72 DDR DRAM MODULE, DMA200 |

| W3E32M64SA-200BI | 32M X 64 DDR DRAM, 0.8 ns, PBGA219 |

| W3EG72256S265JD3MF | 256M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W3EG6462S202D3 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512MB - 2x32Mx64 DDR SDRAM UNBUFFERED |

| W3EG6462S202JD3 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512MB - 2x32Mx64 DDR SDRAM UNBUFFERED |

| W3EG6462S262D3 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512MB - 2x32Mx64 DDR SDRAM UNBUFFERED |

| W3EG6462S262JD3 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512MB - 2x32Mx64 DDR SDRAM UNBUFFERED |

| W3EG6462S263D3 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512MB - 2x32Mx64 DDR SDRAM UNBUFFERED |

发布紧急采购,3分钟左右您将得到回复。