- 您现在的位置:买卖IC网 > PDF目录276890 > W3H64M72E-667ESM (MICROSEMI CORP-PMG MICROELECTRONICS) 64M X 72 DDR DRAM, PBGA208 PDF资料下载

参数资料

| 型号: | W3H64M72E-667ESM |

| 厂商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分类: | DRAM |

| 英文描述: | 64M X 72 DDR DRAM, PBGA208 |

| 封装: | 17 X 23 MM, 1 MM PITCH, PLASTIC, BGA-208 |

| 文件页数: | 3/30页 |

| 文件大小: | 999K |

| 代理商: | W3H64M72E-667ESM |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

W3H64M72E-XSBX

11

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

White Electronic Designs

December 2006

Rev. 2

ADVANCED*

White Electronic Designs Corp. reserves the right to change products or specications without notice.

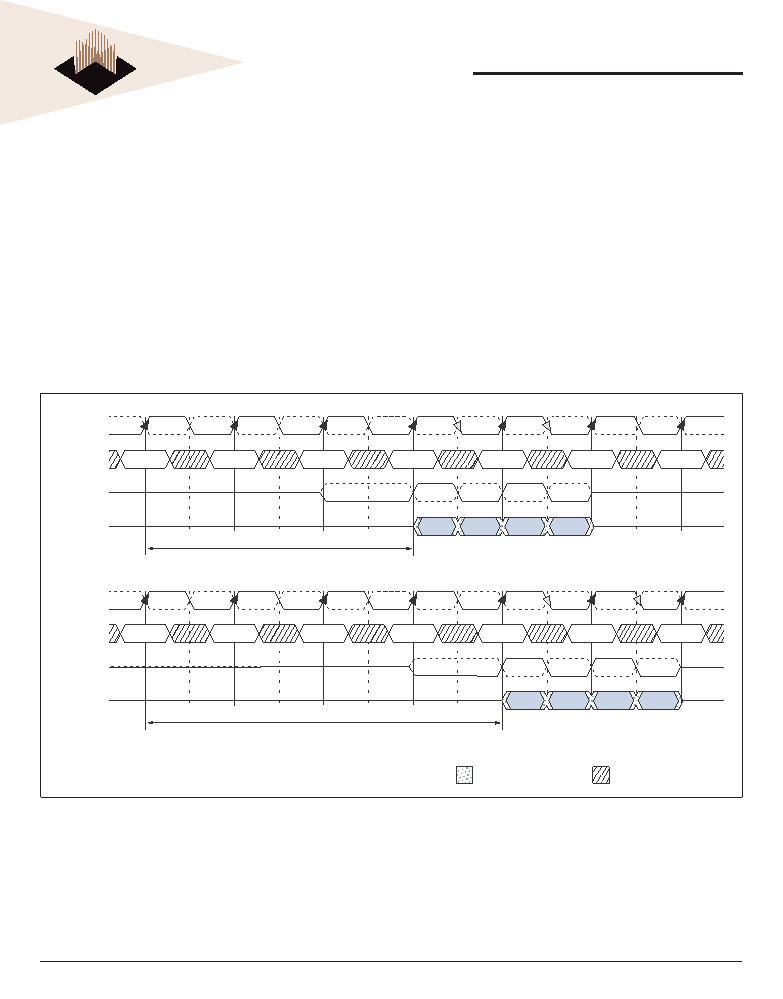

CAS LATENCY (CL)

The CAS latency (CL) is dened by bits M4–M6, as shown

in Figure 5. CL is the delay, in clock cycles, between the

registration of a READ command and the availability of

the rst bit of output data. The CL can be set to 3, 4, 5,

or 6 clocks, depending on the speed grade option being

used.

DDR2 SDRAM does not support any half-clock latencies.

Reserved states should not be used as unknown operation

or incompatibility with future versions may result.

DDR2 SDRAM also supports a feature called posted

CAS additive latency (AL). This feature allows the READ

command to be issued prior to tRCD (MIN) by delaying the

internal command to the DDR2 SDRAM by AL clocks.

Examples of CL = 3 and CL = 4 are shown in Figure 6;

both assume AL = 0. If a READ command is registered

at clock edge n, and the CL is m clocks, the data will be

available nominally coincident with clock edge n+m (this

assumes AL = 0).

DOUT

n + 3

DOUT

n + 2

DOUT

n + 1

CK

CK#

COMMAND

DQ

DQS, DQS#

CL = 3 (AL = 0)

READ

Burst length = 4

Posted CAS# additive latency (AL) = 0

Shown with nominal

t AC, tDQSCK, and tDQSQ

T0

T1

T2

DON’T CARE

TRANSITIONING DATA

NOP

DOUT

n

T3

T4

T5

NOP

T6

NOP

DOUT

n + 3

DOUT

n + 2

DOUT

n + 1

CK

CK#

COMMAND

DQ

DQS, DQS#

CL = 4 (AL = 0)

READ

T0

T1

T2

NOP

DOUT

n

T3

T4

T5

NOP

T6

NOP

FIGURE 6 – CAS LATENCY (CL)

相关PDF资料 |

PDF描述 |

|---|---|

| W3HG32M64EEU665D4MG | 32M X 64 DDR DRAM MODULE, 0.45 ns, ZMA200 |

| W7NCF02GH30CS6FG | 128M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| W7NCF128H20IS9CG | 8M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC |

| WE128K16-150CIA | 128K X 16 EEPROM 5V MODULE, 150 ns, CDMA40 |

| WEDPN8M64V-100B2I | 8M X 64 SYNCHRONOUS DRAM, 7 ns, PBGA219 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W3H64M72E-667SB | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:64M x 72 DDR2 SDRAM 208 PBGA Multi-Chip Package |

| W3H64M72E-667SBC | 制造商:Microsemi Corporation 功能描述:64M X 72 DDR2, 1.8V, 667MHZ, 208PBGA COMMERICAL TEMP. - Bulk |

| W3H64M72E-667SBI | 制造商:Microsemi Corporation 功能描述:64M X 72 DDR2, 1.8V, 667MHZ, 208PBGA INDUSTRIAL TEMP. - Bulk |

| W3H64M72E-667SBM | 制造商:Microsemi Corporation 功能描述:64M X 72 DDR2, 1.8V, 667MHZ, 208PBGA MIL-TEMP. - Bulk 制造商:Microsemi Corporation 功能描述:SDRAM MEMORY |

| W3H64M72EERXXXAD7MG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512MB - 64Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP Mini-DIMM |

发布紧急采购,3分钟左右您将得到回复。