- 您现在的位置:买卖IC网 > PDF目录276891 > W3HG264M72EER806PD4MG (WHITE ELECTRONIC DESIGNS CORP) 128M X 72 DDR DRAM MODULE, DMA200 PDF资料下载

参数资料

| 型号: | W3HG264M72EER806PD4MG |

| 厂商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分类: | DRAM |

| 英文描述: | 128M X 72 DDR DRAM MODULE, DMA200 |

| 封装: | ROHS COMPLIANT, SO-RDIMM-200 |

| 文件页数: | 10/12页 |

| 文件大小: | 228K |

| 代理商: | W3HG264M72EER806PD4MG |

W3HG264M72EER-PD4

February 2007

Rev. 0

7

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

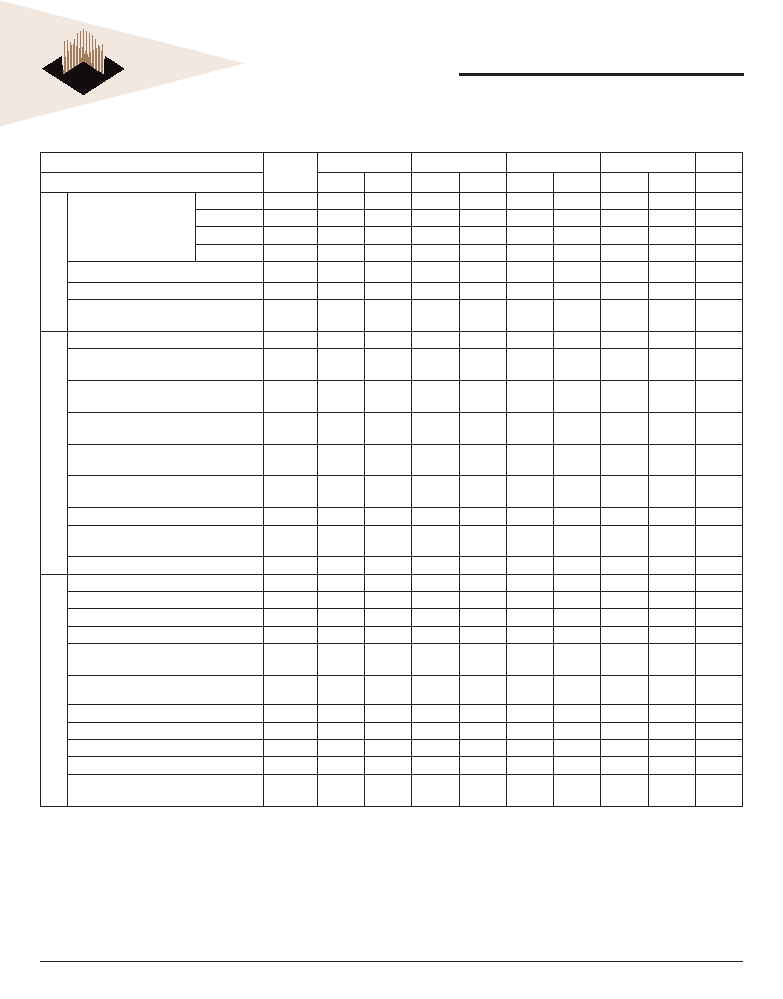

DDR2 SDRAM COMPONENT AC TIMING PARAMETERS & SPECIFICATIONS

AC CHARACTERISTICS

SYMBOL

806

665

534

403

PARAMETER

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

UNIT

Clock

Clock cycle time

CL = 6

tCK (6)

TBD

ps

CL =5

tCK (5)

TBD

3,000

8,000

3,750

8,000

5,000

8,000

ps

CL = 4

tCK (4)

TBD

3,750

8,000

3,750

8,000

5,000

8,000

ps

CL = 3

tCK (3)

TBD

5,000

8,000

5,000

8,000

5,000

8,000

ps

CK high-level width

tCH

TBD

0.45

0.55

0.45

0.55

0.45

0.55

tCK

CK low-level width

tCL

TBD

0.45

0.55

0.45

0.55

0.45

0.55

tCK

Half clock period

tHP

TBD

MIN (tCH,

tCL)

MIN (tCH,

tCL)

MIN (tCH,

tCL)

ps

Data

DQ output access time from CK/CK#

tAC

TBD

-450

+450

-500

+500

-600

+600

ps

Data-out high-impedance window from

CK/CK#

tHZ

TBD

tAC MAX

ps

Data-out low-impedance window from

CK/CK#

tLZ

TBD

2x

tAC MIN

tAC MAX tAC MIN tAC MAX tAC MIN tAC MAX

ps

DQ and DM input setup time relative to

DQS

tDS

TBD

100

150

ps

DQ and DM input hold time relative to

DQS

tDH

TBD

175

225

275

ps

A DQ and DM input pulse width (for each

input)

tDIPW

TBD

0.35

tCK

Data hold skew factor

tQHS

TBD

340

400

450

ps

DQ - DQS hold, DQS to rst DQ to go

nonvalid, per access

tQH

TBD

tHP - tQHS

ps

Data valid output window (DVW)

tDVW

TBD

tQH - tDQSQ

ns

Data

Strobe

DQS input high pulse width

tDQSH

TBD

0.35

tCK

DQS input low pulse width

tDQSL

TBD

0.35

tCK

DQS output access time from CK/CK#

tDQSCK

TBD

-400

+400

-450

+450

-500

+500

ps

DQS falling edge to CK rising - setup time

tDSS

TBD

0.2

tCK

DQS falling edge from CK rising - hold

time

tDSH

TBD

0.2

tCK

DQS - DQ skew, DQS to last DQ valid,

per group, per access

tDQSQ

TBD

240

300

350

ps

DQS read preamble

tRPRE

TBD

0.9

1.1

0.9

1.1

0.9

1.1

tCK

DQS read postamble

tRPST

TBD

0.4

0.6

0.4

0.6

0.4

0.6

tCK

DQS write preamble

tWPRE

TBD

0.35

0.25

tCK

DQS write postamble

tWPST

TBD

0.4

0.6

0.4

0.6

0.4

0.6

tCK

Write command to rst DQS latching

transition

tDQSS

TBD

WL

- 0.25

WL +

0.25

WL

- 0.25

WL +

0.25

WL

- 0.25

WL +

0.25

tCK

Continued on next page

Note: AC specication is based on

QIMONDA components. Other DRAM manufactures specication may be different

相关PDF资料 |

PDF描述 |

|---|---|

| W3E32M64SA-200BI | 32M X 64 DDR DRAM, 0.8 ns, PBGA219 |

| W3EG72256S265JD3MF | 256M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| W3EG7232S202AD4S | 32M X 72 DDR DRAM MODULE, 0.75 ns, DMA200 |

| W3EG7232S202BD4IMG | 32M X 72 DDR DRAM MODULE, 0.75 ns, DMA200 |

| W3EG7232S262AD4ISG | 32M X 72 DDR DRAM MODULE, 0.75 ns, DMA200 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W3HG264M72EER-AD7 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:1GB - 2x64Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP Mini-DIMM |

| W3HG264M72EERXXXAD7MG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:1GB - 2x64Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP Mini-DIMM |

| W3HG264M72EERXXXAD7SG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:1GB - 2x64Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP Mini-DIMM |

| W3HG64M72EER403AD7XG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512MB - 64Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP Mini-DIMM |

| W3HG64M72EER534AD7XG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512MB - 64Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP Mini-DIMM |

发布紧急采购,3分钟左右您将得到回复。