- 您现在的位置:买卖IC网 > PDF目录68459 > W3HG64M72EER534PD4SG (WHITE ELECTRONIC DESIGNS CORP) 64M X 72 DDR DRAM MODULE, 0.5 ns, DMA200 PDF资料下载

参数资料

| 型号: | W3HG64M72EER534PD4SG |

| 厂商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分类: | DRAM |

| 英文描述: | 64M X 72 DDR DRAM MODULE, 0.5 ns, DMA200 |

| 封装: | ROHS COMPLIANT, SO-RDIMM-200 |

| 文件页数: | 2/13页 |

| 文件大小: | 249K |

| 代理商: | W3HG64M72EER534PD4SG |

W3HG64M72EER-PD4

February 2007

Rev. 0

10

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

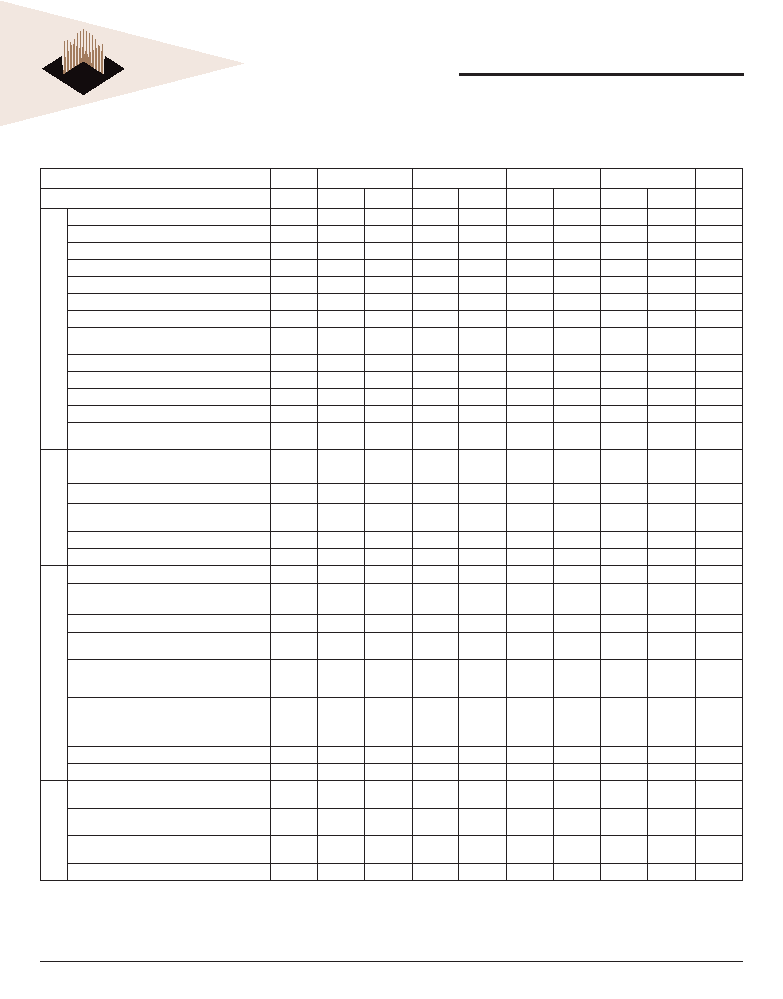

DDR2 SDRAM COMPONT AC TIMING PARAMETERS & SPECIFICATIONS (cont'd)

VCC = +1.8V ± 0.1V

AC CHARACTERISTICS

806

665

534

403

PARAMETER

SYMBOL

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

UNIT

Command

and

Address

ACTIVE to ACTIVE (same bank) command

tRC

TBD

60

55

ns

ACTIVE bank a to ACTIVE bank b command

tRRD

TBD

7.5

ns

ACTIVE to READ or WRITE delay

tRCD

TBD

15

ns

Four Bank Activate period

tFAW

TBD

37.5

ns

ACTIVE to PRECHARGE command

tRAS

TBD

40

70,000

40

70,000

40

70,000

ns

Internal READ to precharge command delay

tRTP

TBD

7.5

ns

Write recovery time

tWR

TBD

15

ns

Auto precharge write recovery + precharge

time

tDAL

TBD

tWR+tRP

ns

Internal WRITE to READ command delay

tWTR

TBD

7.5

10

ns

PRECHARGE command period

tRP

TBD

15

ns

PRECHARGE ALL command period

tRPA

TBD

tRP+tCK

ns

LOAD MODE command cycle time

tMRD

TBD

22

2

tCK

CKE low to CK,CK# uncertainty

tDELAY

TBD

tIS+tCK

tIH

tIS+tCK

tIH

tIS+tCK

tIH

ns

Self

Refresh

REFRESH to Active of Refresh to Refresh

command interfal

tRFC

TBD

105

70,000

105

70,000

105

70,000

ns

Average periodic refresh interval

tREFI

TBD

7.8

μs

Exit self refresh to non-READ command

tXSNR

TBD

tRFC(MIN)

+10

tRFC(MIN)

+10

tRFC(MIN)

+10

ns

Exit self refresh to READ command

tXSRD

TBD

200

tCK

Exit self refresh timing reference

tISXR

TBD

tIS

ps

ODT

ODT turn-on delay

tAOND

TBD

2

22222

tCK

ODT turn-on

tAON

TBD

tAC(MIN)

tAC(MAX)

+1000

tAC(MIN)

tAC(MAX)

+1000

tAC(MIN)

tAC(MAX)

+1000

ps

ODT turn-off delay

tAOFD

TBD

2.5

tCK

ODT turn-off

tAOF

TBD

tAC(MIN)

tAC(MAX)

+600

tAC(MIN)

tAC(MAX)

+600

tAC(MIN)

tAC(MAX)

+600

ps

ODT turn-on (power-down mode)

tAONPD

TBD

tAC(MIN)

+2000

2 x tCK+

tAC(MIN)

+1000

tAC(MIN)

+2000

2 x tCK+

tAC(MIN)

+1000

tAC(MIN)

+2000

2 x tCK+

tAC(MIN)

+1000

ps

ODT turn-off (power-down mode)

tAOFPD

TBD

tAC(MIN)

+2000

2.5 x

tCK+

tAC(MIN)

+1000

tAC(MIN)

+2000

2.5 x

tCK+

tAC(MIN)

+1000

tAC(MIN)

+2000

2.5 x

tCK+

tAC(MIN)

+1000

ps

ODT to power-down entry latency

tANPD

TBD

33

3

tCK

ODT power-down exit latency

tAXPD

TBD

88

8

tCK

Power-Down

Exit active power-down to READ command,

MR[bit12=0]

tXARD

TBD

22

2

tCK

Exit active power-down to READ command,

MR[bit12=1]

tXARDS

TBD

7-AL

6-AL

tCK

A Exit precharge power-down to any non-

READ command.

tXP

TBD

22

2

tCK

CKE minimum high/low time

tCKE

TBD

33

3

tCK

* AC specication is based on

SAMSUNG components. Other DRAM manufactures specication may be different.

相关PDF资料 |

PDF描述 |

|---|---|

| W3HG64M72EER665PD4MG | 64M X 72 DDR DRAM MODULE, 0.45 ns, DMA200 |

| W3HG64M72EER403PD4ISG | 64M X 72 DDR DRAM MODULE, 0.6 ns, DMA200 |

| W3HG64M72EER806PD4MG | 64M X 72 DDR DRAM MODULE, DMA200 |

| W3HG64M72EER534PD4MG | 64M X 72 DDR DRAM MODULE, 0.5 ns, DMA200 |

| W3HG64M72EEU806PD4GG | 64M X 72 DDR DRAM MODULE, DMA200 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W3HG64M72EER665AD7XG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512MB - 64Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP Mini-DIMM |

| W3HG64M72EER806AD7XG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512MB - 64Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP Mini-DIMM |

| W3HG64M72EER-AD7 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512MB - 64Mx72 DDR2 SDRAM REGISTERED, w/PLL, VLP Mini-DIMM |

| W3J128M72G-1066PBI | 制造商:Microsemi Corporation 功能描述:DRAM MODULE DDR3 SDRAM 9G-BIT - Bulk 制造商:Microsemi Corporation 功能描述:SDRAM MEMORY |

| W3J128M72G-800PBI | 制造商:Microsemi Corporation 功能描述:SDRAM MEMORY |

发布紧急采购,3分钟左右您将得到回复。