- 您现在的位置:买卖IC网 > PDF目录68559 > W982504AH-7 (WINBOND ELECTRONICS CORP) 64M X 4 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 PDF资料下载

参数资料

| 型号: | W982504AH-7 |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | DRAM |

| 英文描述: | 64M X 4 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| 封装: | 0.400 INCH, 0.80 MM PITCH, TSOP2-54 |

| 文件页数: | 1/41页 |

| 文件大小: | 1555K |

| 代理商: | W982504AH-7 |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页

W982504AH

16M

× 4 BANKS × 4 BIT SDRAM

Publication Release Date: March 2001

- 1 -

Revision A3

GENERAL DESCRIPTION

W982504AH is a high-speed synchronous dynamic random access memory (SDRAM), organized as

16M words

× 4 banks × 4 bits. Using pipelined architecture and 0.175 m process technology,

W982504AH delivers a data bandwidth of up to 143M words per second (-7). To fully comply with the

personal computer industrial standard, W982504AH is sorted into three speed grades: -7, -75 and -

8H. The -7 is compliant to the 143 MHz/CL3 or PC133/CL2 specification, the -75 is compliant to the

PC133/CL3 specification, the -8H is compliant to the PC100/CL2 specification.

Accesses to the SDRAM are burst oriented. Consecutive memory location in one page can be

accessed at a burst length of 1, 2, 4, 8 or full page when a bank and row is selected by an ACTIVE

command. Column addresses are automatically generated by the SDRAM internal counter in burst

operation. Random column read is also possible by providing its address at each clock cycle. The

multiple bank nature enables interleaving among internal banks to hide the precharging time.

By having a programmable Mode Register, the system can change burst length, latency cycle,

interleave or sequential burst to maximize its performance. W982504AH is ideal for main memory in

high performance applications.

FEATURES

3.3V

±0.3V Power Supply

Up to 143 MHz Clock Frequency

16,777,216 Words

× 4 banks × 4 bits organization

Auto Refresh and Self Refresh

CAS Latency: 2 and 3

Burst Length: 1, 2, 4, 8, and full page

Burst Read, Single Writes Mode

Byte Data Controlled by DQM

Power-down Mode

Auto-Precharge and Controlled Precharge

8K Refresh Cycles/64 mS

Interface: LVTTL

Packaged in TSOP II 54-pin, 400 mil - 0.80

KEY PARAMETERS

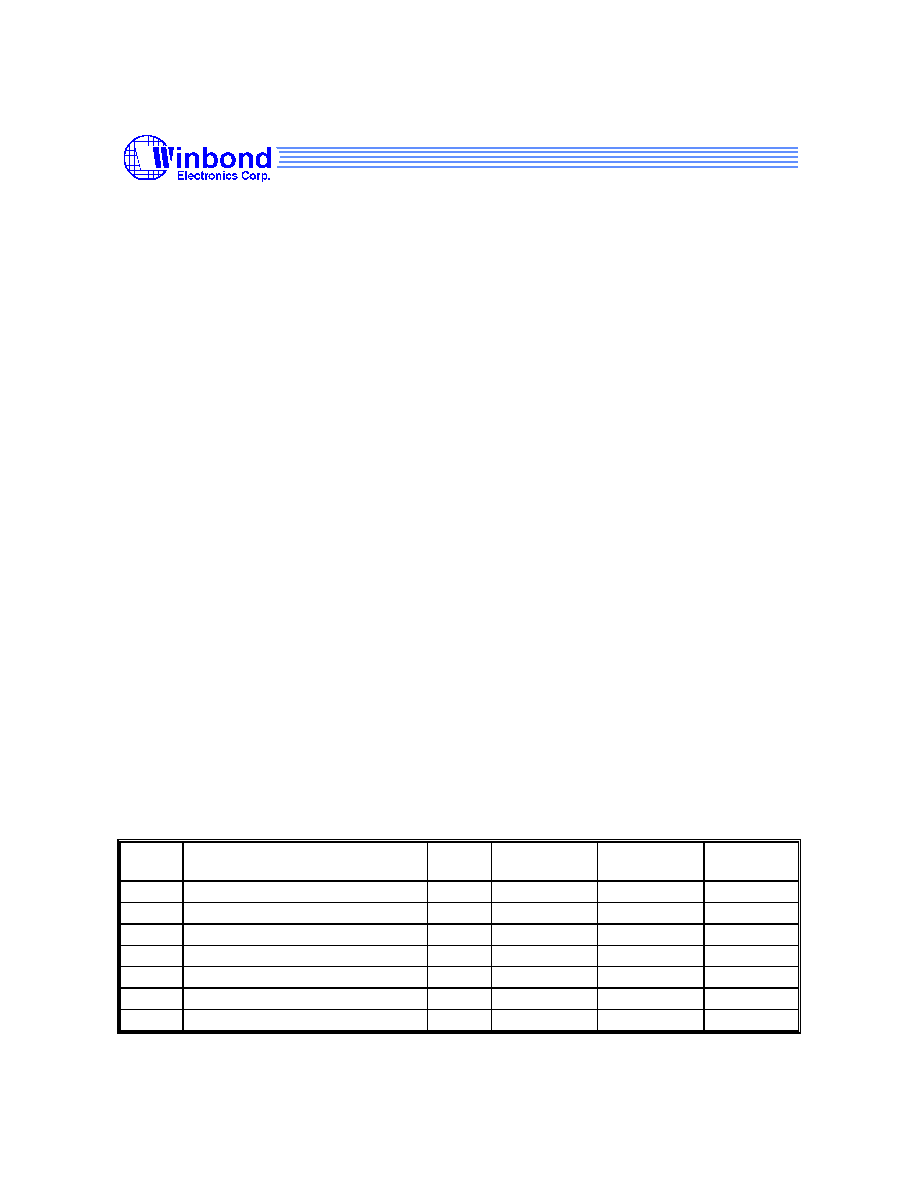

SYM.

DESCRIPTION

MIN.

/MAX.

-7

(PC133, CL2)

-75

(PC133, CL3)

-8H

(PC100)

tCK

Clock Cycle Time

Min.

7 nS

7.5 nS

8 nS

tAC

Access Time from CLK

Max.

5.4 nS

6 nS

tRP

Precharge to Active Command

Min.

15 nS

20 nS

tRCD

Active to Read/Write Command

Min.

15 nS

20 nS

ICC1

Operation Current (Single bank)

Max.

80 mA

75 mA

70 mA

ICC4

Burst Operation Current

Max.

100 mA

95 mA

90 mA

ICC6

Self-Refresh Current

Max.

3 mA

相关PDF资料 |

PDF描述 |

|---|---|

| W982508BH75L | 32M X 8 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| W982516AH-8H | 16M X 16 SYNCHRONOUS DRAM, 6 ns, PDSO54 |

| W9825G2DB-6 | 8M X 32 SYNCHRONOUS DRAM, 5 ns, PBGA90 |

| W9825G6JH-6 | 16M X 16 SYNCHRONOUS DRAM, 5 ns, PDSO54 |

| W9825G6JH-5 | 16M X 16 SYNCHRONOUS DRAM, 5 ns, PDSO54 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W982504AH-75 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x4 SDRAM |

| W982504AH-8H | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x4 SDRAM |

| W982508AH | 制造商:WINBOND 制造商全称:Winbond 功能描述:8M X 4 BANKS X 8 BIT SDRAM |

| W982508AH-7 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 SDRAM |

| W982508AH-75 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 SDRAM |

发布紧急采购,3分钟左右您将得到回复。