- 您现在的位置:买卖IC网 > PDF目录140420 > WED2ZLRSP01S38BI (WHITE ELECTRONIC DESIGNS CORP) 512K X 32 MULTI DEVICE SRAM MODULE, 3.8 ns, PBGA209 PDF资料下载

参数资料

| 型号: | WED2ZLRSP01S38BI |

| 厂商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分类: | SRAM |

| 英文描述: | 512K X 32 MULTI DEVICE SRAM MODULE, 3.8 ns, PBGA209 |

| 封装: | PLASTIC, BGA-209 |

| 文件页数: | 1/13页 |

| 文件大小: | 351K |

| 代理商: | WED2ZLRSP01S38BI |

1

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

White Electronic Designs

WED2ZLRSP01S

April, 2002

Rev. 0

White Electronic Designs Corp. reserves the right to change products or specications without notice.

The WED2ZLRSP01S, Dual Independent Array, NBL-

SSRAM device employs high-speed, Low-Power CMOS

silicon and is fabricated using an advanced CMOS process.

WEDC’s 24Mb, Sync Burst SRAM MCP integrates two

totally independent arrays, the rst organized as a 512K x

32, and the second a 256K x 32.

All Synchronous inputs pass through registers controlled

by a positive edge triggered, single clock input per array.

The NBL or No Bus Latency Memory provides 100% bus

utilizaton, with no loss of cycles caused by change in modal

operation (Write to Read/Read to Write). All inputs except

for Asynchronous Output Enable and Burst Mode control

are synchronized on the positive or rising edge of Clock.

Burst order control must be tied either HIGH or LOW, Write

cycles are internally self-timed, and writes are initiated on

the rising edge of clock. This feature eliminates the need

for complex off-chip write pulse generation and proved

increased timing exibility for incoming signals.

512K x 32/256K x 32 Dual Array

Synchronous Pipeline Burst NBL SRAM

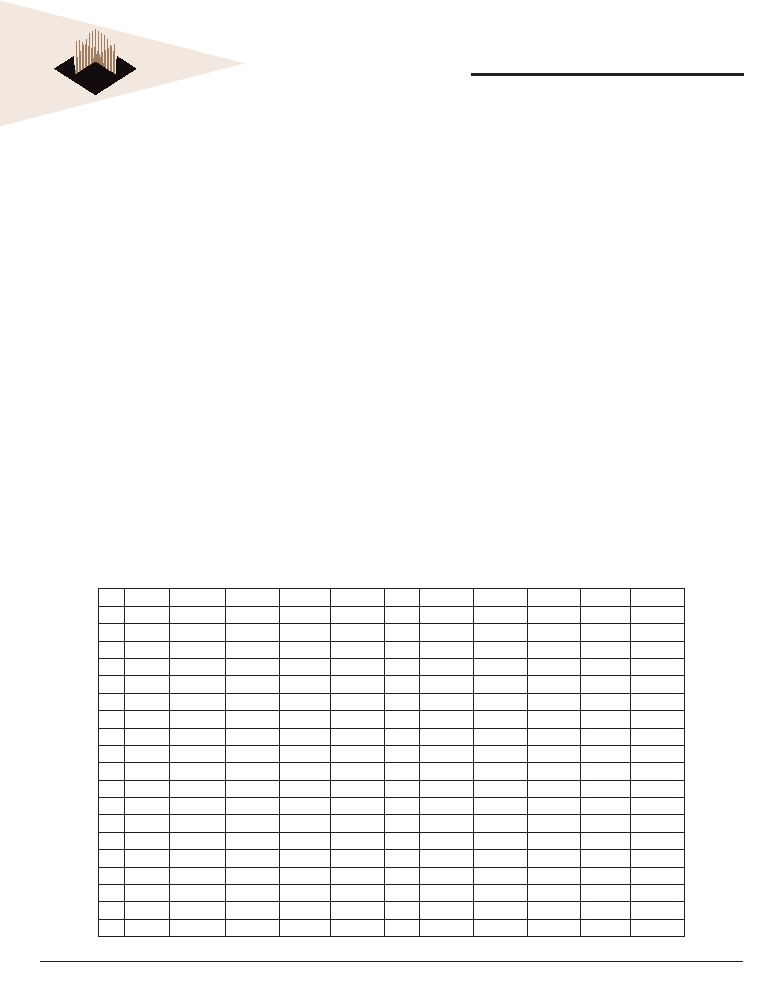

PIN CONFIGURATION

(TOP VIEW)

Fast clock speed: 166, 150, 133, and 100MHz

Fast access times: 3.5ns, 3.8ns, 4.2ns, and 5.0ns

Fast OE# access times: 3.5ns, 3.8ns, 4.2ns, and

5.0ns

Single +2.5V ± 5% power supply (VCC)

Snooze Mode for reduced-standby power

Individual Byte Write control

Clock-controlled and registered addresses, data

I/Os and control signals

Burst control (interleaved or linear burst)

Packaging:

209-bump BGA package

Low capacitive bus loading

12

3

4

5

6

7

8

9

10

11

A

Vss

A_DATb0

A_DATb1

A_DATb2

A_DATb3

Vss

A_DATa0

A_DATa1

A_DATa2

A_DATa3

Vss

B

NC

A_DATb4

A_DATb5

A_DATb6

A_DATb7

Vss

A_DATa4

A_DATa5

A_DATa6

A_DATa7

NC

C

A_ADR

A_OE#

A_ADV

A_BWEb

Vss

A_BWEa

A_ZZ

A_ADR

D

A_ADR

Vss

A_CKE#

Vcc

A_ADR

E

A_ADR

A_CK

A_GWE#

Vcc

A_ADR1

A_ADR0

F

A_ADR

Vss

A_CS2#

Vcc

A_ADR

G

A_ADR

A_CS1#A_CS2

A_BWEc

Vss

A_BWEd

A_LBO#

A_ADR

H

NC

A_DATc0

A_DATc1

A_DATc2

A_DATc3

Vss

A_DATd0

A_DATd1

A_DATd2

A_DATd3

NC

J

Vss

A_DATc4

A_DATc5

A_DATc6

A_DATc7

Vss

A_DATd4

A_DATd5

A_DATd6

A_DATd7

Vss

K

Vss

L

Vss

B_DATb0

B_DATb1

B_DATb2

B_DAT3

Vss

B_DATa0

B_DATa1

B_DATa2

B_DATa3

Vss

M

NC

B_DATb4

B_DATb5

B_DATb6

B_DAT7

Vss

B_DATa4

B_DATa5

B_DATa6

B_DATa7

NC

N

B_ADR

B_OE#

B_ADV

B_BWEb

Vss

B_BWEa

B_ZZ

B_ADR

P

B_ADR

Vss

B_CKE#

Vcc

B_ADR

R

B_ADR

B_CK

B_GWE#

Vcc

B_ADR1

B_ADR0

T

B_ADR

Vss

B_CS2#

Vcc

B_ADR

U

B_ADR

NC

B_CS1#

B_CS2

B_BWEc

Vss

B_BWEd

B_LBO#

B_ADR

V

NC

B_DATc4

B_DATc5

B_DATc6

B_DATc7

Vss

B_DATd4

B_DATd5

B_DATd6

B_DATd7

NC

W

Vss

B_DATc0

B_DATc1

B_DATc2

B_DATc3

Vss

B_DATd0

B_DATd1

B_DATd2

B_DATd3

Vss

FEATURES

DESCRIPTION

相关PDF资料 |

PDF描述 |

|---|---|

| WF512K32N-90H1Q5A | 512K X 32 FLASH 5V PROM MODULE, 90 ns, CPGA66 |

| WF512K32-120G1TQ5 | 512K X 32 FLASH 5V PROM MODULE, 120 ns, CQFP68 |

| WF512K32-150G1TC5A | 512K X 32 FLASH 5V PROM MODULE, 150 ns, CQFP68 |

| WF512K32-60G1TI5 | 512K X 32 FLASH 5V PROM MODULE, 60 ns, CQFP68 |

| WV3EG264M64EFSU335D4MG | 128M X 64 DDR DRAM MODULE, 0.7 ns, DMA200 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| WED2ZLRSP01S42BC | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512K x 32/256K x 32 Dual Array Synchronous Pipeline Burst NBL SRAM |

| WED2ZLRSP01S42BI | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512K x 32/256K x 32 Dual Array Synchronous Pipeline Burst NBL SRAM |

| WED2ZLRSP01S50BC | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512K x 32/256K x 32 Dual Array Synchronous Pipeline Burst NBL SRAM |

| WED2ZLRSP01S50BI | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:512K x 32/256K x 32 Dual Array Synchronous Pipeline Burst NBL SRAM |

| WED2ZLRSP01S-BC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:NBL SSRAM MCP |

发布紧急采购,3分钟左右您将得到回复。