- 您现在的位置:买卖IC网 > PDF目录140424 > WED3DG6435V7D1-MG (WHITE ELECTRONIC DESIGNS CORP) 32M X 64 SYNCHRONOUS DRAM MODULE, 5.4 ns, DMA144 PDF资料下载

参数资料

| 型号: | WED3DG6435V7D1-MG |

| 厂商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分类: | DRAM |

| 英文描述: | 32M X 64 SYNCHRONOUS DRAM MODULE, 5.4 ns, DMA144 |

| 封装: | ROHS COMPLIANT, SODIMM-144 |

| 文件页数: | 5/8页 |

| 文件大小: | 158K |

| 代理商: | WED3DG6435V7D1-MG |

WED3DG6435V-D1

-JD1

5

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

June 2007

Rev. 8

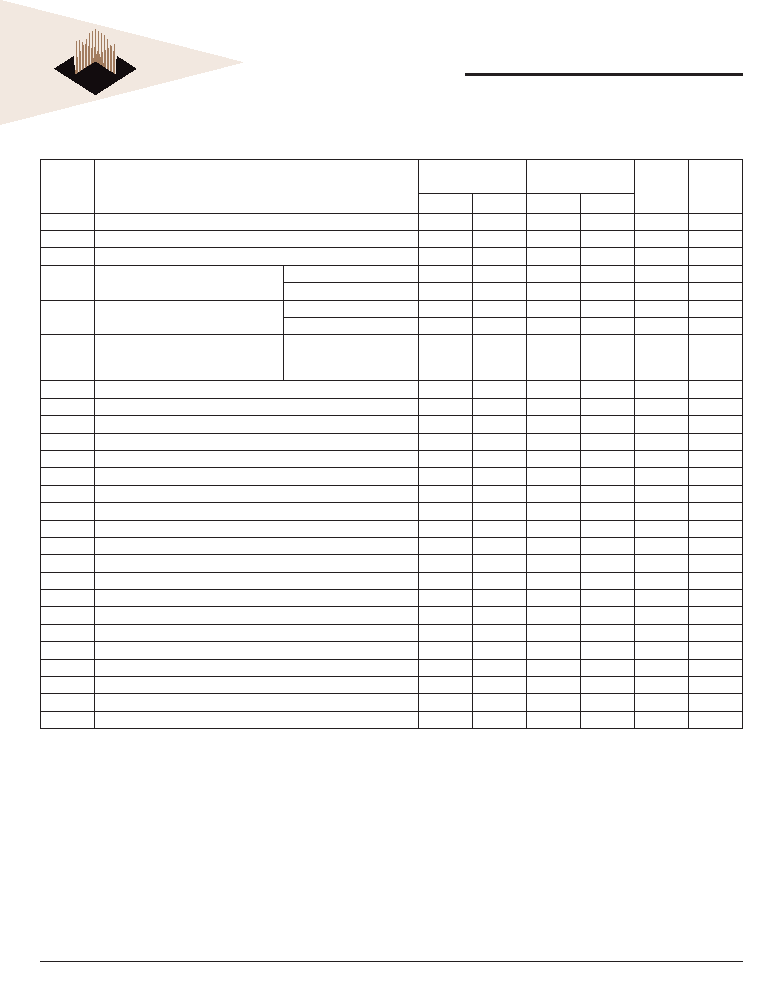

AC TIMING PARAMETERS

Symbol

Parameter

Speed Grade

100MHz

Speed Grade

133MHz

Units

Notes

Min

Max

Min

Max

tCK

Clock Period

10

7.5

ns

tCH

Clock High Time Rated @1.5V

3

2.5

ns

tCL

Clock Low Time

3

2.5

ns

tIS

Input Setup Times

Address/ Command & CKE

2

1.5

ns

Data

2

1.5

ns

tIH

Input Hold Times

Address/Command & CKE

1

0.8

ns

Data

1

0.8

ns

tAC

Output Valid From Clock

CAS# Latency = 2 or 3,

LVTTL levels, Rated @ 50

pF all outputs switching

5.4

(tco = 5.2)

5.4

(tco = 4.6)

ns

1

tOH

Output Hold From Clock Rated @ 50 pF (1.8 ns @ 0 pf)

3

ns

tOHZ

Output Valid to Z

3736

ns

tCCD

CAS to CAS Delay

1

tCK

tRP

RAS Precharge Time

15

ns

tRAS

RAS Active Time

37

ns

tRCD

Activate to Command Delay (RAS to CAS Delay)

15

ns

tRRD

RAS to RAS Bank Activate Delay

14

ns

tRC

RAS Cycle Time

60

ns

tDQD

DQM to Input Data Delay

0

tCK

tRSC

Mode Register set to Active delay

2

tCK

tROH

Precharge to O/P in High Z

CL = 2(2) (3) CL = 3 (2) CL = 2 3 CL = 3

tCK

2

tDQZ

DQM to Data in High Z for read

2222

tCK

tDQM

DQM to Data mask for write

0

tCK

3

tDPL

Data-in to PRE Command Period

2

tCK

tDAL

Data-in to ACT (PRE) Command period (Auto precharge)

4

tCK

tSB

Power Down Mode Entry

8

7

1

ns

tSRX

Self Refresh Exit Time

1

tCK

tPDE

Power Down Exit Set up Time

1

tCK

5

tREF

Refresh Period

64

ms

tRFC

Row Refresh Cycle Time

63

66

ns

1.

Access times to be measured w/input signals of 1 V/ns edge rate, 0.8 V to 2.0 V, tCO is clock to output with no load.

2.

CL = CAS Latency

3.

Data Masked on the same clock

4.

Self refresh Exit is asynchronous, requiring 10 ns to ensure initiation. Self refresh exit is complete in 10 ns + tRC.

5.

Timing is asynchronous. If tIS is not met by rising edge of CK then CKE is assumed latched on next cycle.

6.

If the clock is stopped during self refresh or power down, 200 clocks are required before CKE is high.

相关PDF资料 |

PDF描述 |

|---|---|

| W332M64V-125SBI | 32M X 64 SYNCHRONOUS DRAM, 6 ns, PBGA208 |

| W3DG6432V7D2 | 32M X 64 SYNCHRONOUS DRAM MODULE, DMA168 |

| W3EG7234S262AJD3 | 32M X 72 DDR DRAM MODULE, DMA184 |

| W3EG7234S265JD3 | 32M X 72 DDR DRAM MODULE, DMA184 |

| W3EG7266S335BD4IG | 64M X 72 DDR DRAM MODULE, 0.7 ns, DMA200 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| WED3DG6435V7JD1 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:256MB - 32Mx64 SDRAM UNBUFFERED |

| WED3DG6435V-AD1 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:256MB - 32Mx64 SDRAM UNBUFFERED |

| WED3DG6435V-D1 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:256MB - 32Mx64 SDRAM UNBUFFERED |

| WED3DG6435V-D2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SDRAM Modules - 168 Pin DIMM. Unbuffered |

| WED3DG6435V-JD1 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:256MB - 32Mx64 SDRAM UNBUFFERED |

发布紧急采购,3分钟左右您将得到回复。