- 您现在的位置:买卖IC网 > PDF目录276857 > WV3HG2128M72EEU806AD4-SG (MICROSEMI CORP-PMG MICROELECTRONICS) 256M X 72 DDR DRAM MODULE, ZMA200 PDF资料下载

参数资料

| 型号: | WV3HG2128M72EEU806AD4-SG |

| 厂商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分类: | DRAM |

| 英文描述: | 256M X 72 DDR DRAM MODULE, ZMA200 |

| 封装: | ROHS COMPLIANT, SODIMM-200 |

| 文件页数: | 8/11页 |

| 文件大小: | 195K |

| 代理商: | WV3HG2128M72EEU806AD4-SG |

WV3HG2128M72EEU-AD4

October 2006

Rev. 1

ADVANCED

6

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

White Electronic Designs

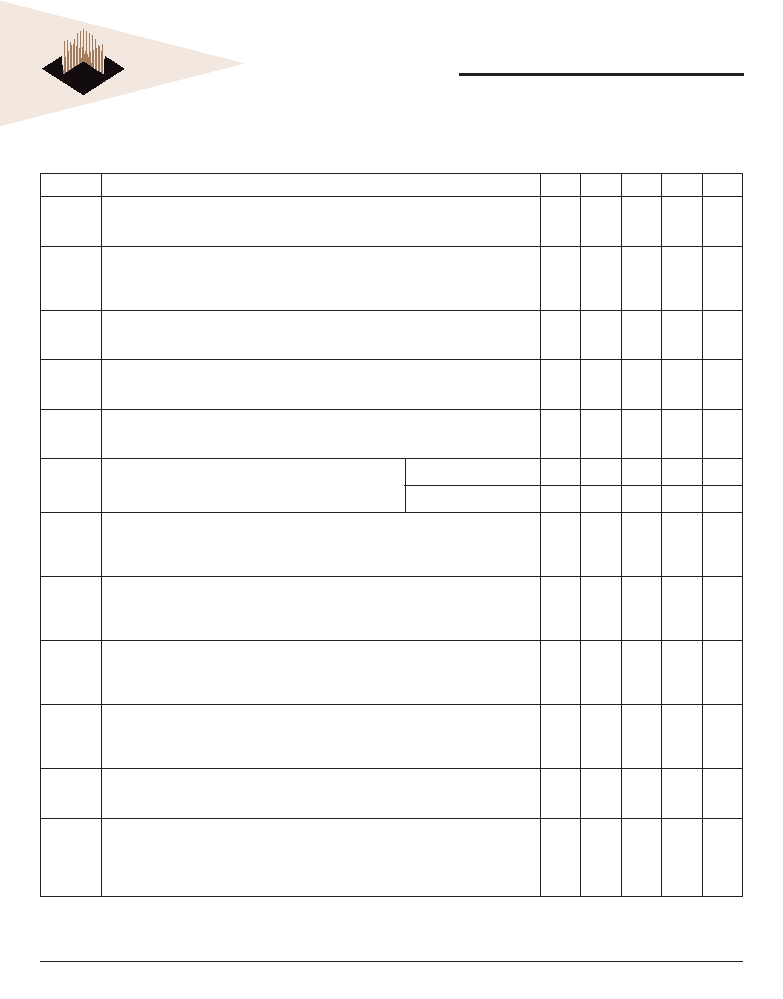

DDR2 ICC SPECIFICATIONS AND CONDITIONS

Includes DDR2 SDRAM components only

0°C ≤ TCASE < +70°C; VCCQ = + 1.8V ± 0.1V, VCC = +1.8V ± 0.1V

Symbol

Proposed Conditions

806

665

534

403

Units

ICC0*

Operating one bank active-precharge current;

tCK = tCK(ICC), tRC = tRC(ICC), tRAS = tRASmin(ICC); CKE is HIGH, CS# is HIGH between valid

commands; Address bus inputs are SWITCHING; Data bus inputs are SWITCHING

TBD

1,218

1,173

1,128

mA

ICC1*

Operating one bank active-read-precharge current;

IOUT = 0mA; BL = 4, CL = CL(ICC), AL = 0; tCK = tCK(ICC), tRC = tRC (ICC), tRAS = tRASmin(ICC), tRCD

= tRCD(ICC); CKE is HIGH, CS# is HIGH between valid commands; Address bus inputs are

SWITCHING; Data pattern is same as ICC4W

TBD

1,308

1,263

1,218

mA

ICC2P**

Precharge power-down current;

All banks idle; tCK = tCK(ICC); CKE is LOW; Other control and address bus inputs are STABLE;

Data bus inputs are FLOATING

TBD

516

mA

ICC2Q**

Precharge quiet standby current;

All banks idle; tCK = tCK(ICC); CKE is HIGH, CS# is HIGH; Other control and address bus inputs

are STABLE; Data bus inputs are FLOATING

TBD

1,020

930

mA

ICC2N**

Precharge standby current;

All banks idle; tCK = tCK(ICC); CKE is HIGH, CS# is HIGH; Other control and address bus inputs

are SWITCHING; Data bus inputs are SWITCHING

TBD

1,110

1,020

mA

ICC3P**

Active power-down current;

All banks open; tCK = tCK(ICC); CKE is LOW; Other control and

address bus inputs are STABLE; Data bus inputs are FLOATING

Fast PDN Exit MRS(12) = 0

TBD

840

750

mA

Slow PDN Exit MRS(12) = 1

TBD

516

mA

ICC3N**

Active standby current;

All banks open; tCK = tCK(ICC), tRAS = tRASmax(ICC), tRP = tRP(ICC); CKE is HIGH, CS# is HIGH

between valid commands; Other control and address bus inputs are SWITCHING; Data bus

inputs are SWITCHING

TBD

1,200

1,110

mA

ICC4W*

Operating burst write current;

All banks open, Continuous burst writes; BL = 4, CL = CL(ICC), AL = 0; tCK = tCK(ICC), tRAS =

tRASmax(ICC), tRP = tRP(ICC); CKE is HIGH, CS# is HIGH between valid commands; Address bus

inputs are SWITCHING; Data bus inputs are SWITCHING

TBD

1,803

1,578

1,443

mA

ICC4R*

Operating burst read current;

All banks open, Continuous burst reads, IOUT = 0mA; BL = 4, CL = CL(ICC), AL = 0; tCK = tCK(ICC),

tRAS = tRASmax(ICC), tRP = tRP(ICC); CKE is HIGH, CS# is HIGH between valid commands; Address

bus inputs are SWITCHING; Data pattern is same as ICC4W

TBD

1,803

1,578

1,443

mA

ICC5**

Burst auto refresh current;

tCK = tCK(ICC); Refresh command at every tRFC(ICC) interval; CKE is HIGH, CS# is HIGH between

valid commands; Other control and address bus inputs are SWITCHING; Data bus inputs are

SWITCHING

TBD

4,260

4,170

4,080

mA

ICC6**

Self refresh current;

CK and CK\ at 0V; CKE 0.2V; Other control and address bus inputs

are FLOATING; Data bus inputs are FLOATING

TBD

108

mA

ICC7*

Operating bank interleave read current;

All bank interleaving reads, IOUT = 0mA; BL = 4, CL = CL(ICC), AL = tRCD(ICC)-1*tCK(ICC); tCK =

tCK(ICC), tRC = tRC(ICC), tRRD = tRRD(ICC), tRCD = 1*tCK(ICC); CKE is HIGH, CS# is HIGH between valid

commands; Address bus inputs are STABLE during DESELECTs; Data pattern is same as ICC4R;

Refer to the following page for detailed timing conditions

TBD

3,108

2,928

2,748

mA

Note: ICC specication is based on

SAMSUNG components. Other DRAM Manufacturers specication may be different.

* Value calculated as one module rank in this operation condition, and all other module ranks in ICC2P (CKE LOW) mode.

** Value calculated reects all module ranks in the operating condition.

相关PDF资料 |

PDF描述 |

|---|---|

| W1D64M72R8A-3.75AE-FA | 64M X 8 DDR DRAM MODULE, 0.5 ns, DMA240 |

| W1D64M72R8A-3.75AE-PB1 | 64M X 8 DDR DRAM MODULE, 0.5 ns, DMA240 |

| W1D64M72R8A-3.75AL-FA2 | 64M X 8 DDR DRAM MODULE, 0.5 ns, DMA240 |

| W1D64M72R8A-3.75AR-QB1 | 64M X 8 DDR DRAM MODULE, 0.5 ns, DMA240 |

| W1D64M72R8A-5AE-PA | 64M X 8 DDR DRAM MODULE, 0.5 ns, DMA240 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| WV3HG2128M72EEU806D6IMG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:2GB - 2x128Mx72 DDR2 SDRAM UNBUFFERED DIMM |

| WV3HG2128M72EEU806D6ISG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:2GB - 2x128Mx72 DDR2 SDRAM UNBUFFERED DIMM |

| WV3HG2128M72EEU806D6MG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:2GB - 2x128Mx72 DDR2 SDRAM UNBUFFERED DIMM |

| WV3HG2128M72EEU806D6SG | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:2GB - 2x128Mx72 DDR2 SDRAM UNBUFFERED DIMM |

| WV3HG2128M72EEU-AD4 | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:2GB - 2x128Mx72 DDR2 SDRAM UNBUFFERED, ECC w/PLL |

发布紧急采购,3分钟左右您将得到回复。