参数资料

| 型号: | X4323S8I-4.5A |

| 厂商: | Intersil |

| 文件页数: | 9/22页 |

| 文件大小: | 0K |

| 描述: | IC SUPERVISOR CPU 32K EE 8-SOIC |

| 标准包装: | 200 |

| 类型: | 简单复位/加电复位 |

| 监视电压数目: | 1 |

| 输出: | 开路漏极或开路集电极 |

| 复位: | 低有效 |

| 复位超时: | 最小为 100 ms |

| 电压 - 阀值: | 4.62V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SO |

| 包装: | 管件 |

�� �

�

�

�X4323,� X4325�

�Writing� to� the� Control� Register�

�Changing� any� of� the� nonvolatile� bits� of� the� control� reg-�

�ister� requires� the� following� steps:�

�–� Write� a� 02H� to� the� Control� Register� to� set� the� Write�

�Enable� Latch� (WEL).� This� is� a� volatile� operation,� so�

�there� is� no� delay� after� the� write.� (Operation� pre-�

�ceeded� by� a� start� and� ended� with� a� stop).�

�–� Write� a� 06H� to� the� Control� Register� to� set� both� the�

�Register� Write� Enable� Latch� (RWEL)� and� the� WEL�

�bit.� This� is� also� a� volatile� cycle.� The� zeros� in� the� data�

�byte� are� required.� (Operation� preceeded� by� a� start�

�and� ended� with� a� stop).�

�–� Write� a� value� to� the� Control� Register� that� has� all� the�

�control� bits� set� to� the� desired� state.� This� can� be� rep-�

�resented� as� 0xys� t� 01� r� in� binary,� where� xy� are� the�

�WD� bits,� and� rst� are� the� BP� bits.� (Operation� pre-�

�ceeded� by� a� start� and� ended� with� a� stop).� Since� this�

�is� a� nonvolatile� write� cycle� it� will� take� up� to� 10ms� to�

�complete.� The� RWEL� bit� is� reset� by� this� cycle� and�

�the� sequence� must� be� repeated� to� change� the� non-�

�volatile� bits� again.� If� bit� 2� is� set� to� ‘1’� in� this� third� step�

�(� 0xys� t� 11� r� )� then� the� RWEL� bit� is� set,� but� the� WD1,�

�WD0,� BP2,� BP1� and� BP0� bits� remain� unchanged.�

�Writing� a� second� byte� to� the� control� register� is� not�

�allowed.� Doing� so� aborts� the� write� operation� and�

�returns� a� NACK.�

�–� A� read� operation� occurring� between� any� of� the�

�previous� operations� will� not� interrupt� the� register�

�write� operation.�

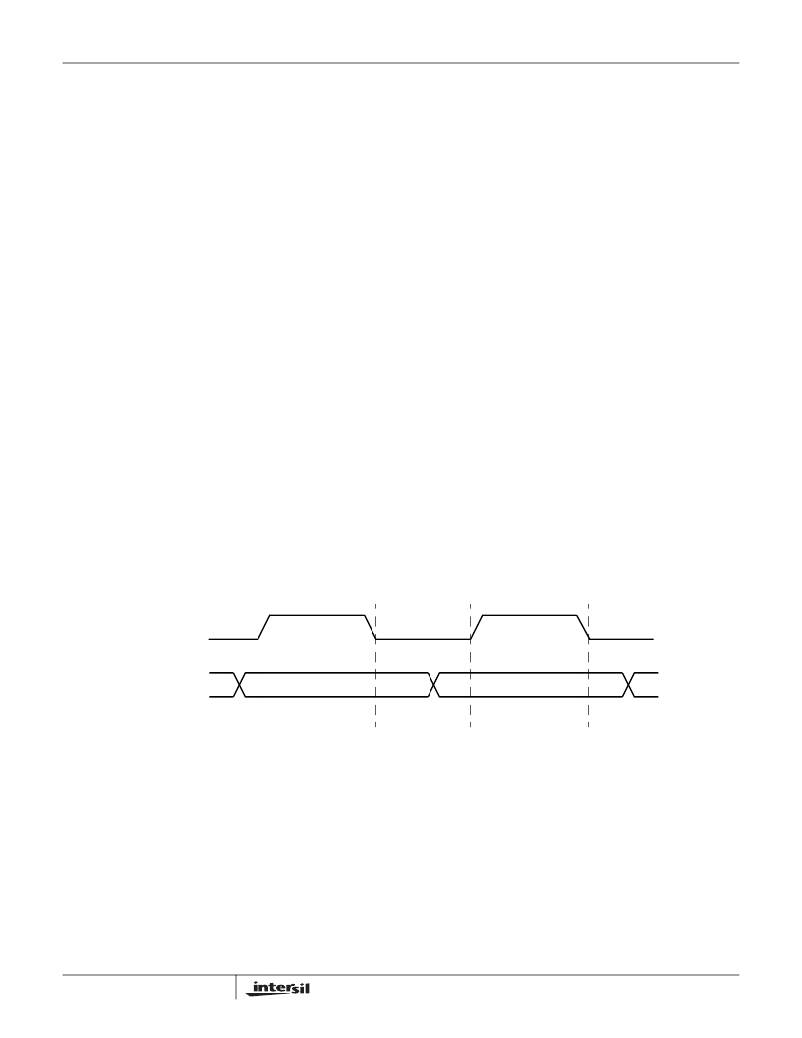

�Figure� 5.� Valid� Data� Changes� on� the� SDA� Bus�

�SCL�

�SDA�

�–� The� RWEL� bit� cannot� be� reset� without� writing� to� the�

�nonvolatile� control� bits� in� the� control� register,� power�

�cycling� the� device� or� attempting� a� write� to� a� write�

�protected� block.�

�To� illustrate,� a� sequence� of� writes� to� the� device� con-�

�sisting� of� [02H,� 06H,� 02H]� will� reset� all� of� the� nonvola-�

�tile� bits� in� the� Control� Register� to� 0.� A� sequence� of�

�[02H,� 06H,� 06H]� will� leave� the� nonvolatile� bits�

�unchanged� and� the� RWEL� bit� remains� set.�

�SERIAL� INTERFACE�

�Serial� Interface� Conventions�

�The� device� supports� a� bidirectional� bus� oriented� proto-�

�col.� The� protocol� defines� any� device� that� sends� data�

�onto� the� bus� as� a� transmitter,� and� the� receiving� device�

�as� the� receiver.� The� device� controlling� the� transfer� is�

�called� the� master� and� the� device� being� controlled� is�

�called� the� slave.� The� master� always� initiates� data�

�transfers,� and� provides� the� clock� for� both� transmit� and�

�receive� operations.� Therefore,� the� devices� in� this� fam-�

�ily� operate� as� slaves� in� all� applications.�

�Serial� Clock� and� Data�

�Data� states� on� the� SDA� line� can� change� only� during�

�SCL� LOW.� SDA� state� changes� during� SCL� HIGH� are�

�reserved� for� indicating� start� and� stop� conditions.� See�

�Figure� 5.�

�9�

�Data� Stable�

�Data� Change�

�Data� Stable�

�FN8122.1�

�May� 25,� 2006�

�相关PDF资料 |

PDF描述 |

|---|---|

| P1812-224K | INDUCTOR POWER 220UH SMD |

| ESM24DTAI-S189 | CONN EDGECARD 48POS R/A .156 SLD |

| UUR1E331MNL1GS | CAP ALUM 330UF 25V 20% SMD |

| X4323S8I-2.7A | IC SUPERVISOR CPU 32K EE 8-SOIC |

| NCP5314MNR2 | IC CTRLR BUCK CPU 2/3/4PH 32QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X4323S8IZ | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 32k EEPROM |

| X4323S8IZ-2.7 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 32k EEPROM |

| X4323S8IZ-2.7A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 32k EEPROM |

| X4323S8IZ-4.5A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 32k EEPROM |

| X4323S8Z | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 32k EEPROM |

发布紧急采购,3分钟左右您将得到回复。