参数资料

| 型号: | X4323V8I-4.5A |

| 厂商: | Intersil |

| 文件页数: | 11/22页 |

| 文件大小: | 0K |

| 描述: | IC SUPERVISOR CPU 32K EE 8-TSSOP |

| 标准包装: | 200 |

| 类型: | 简单复位/加电复位 |

| 监视电压数目: | 1 |

| 复位: | 低有效 |

| 复位超时: | 最小为 100 ms |

| 电压 - 阀值: | 4.62V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 8-TSSOP |

| 包装: | 管件 |

�� �

�

�

�X4323,� X4325�

�Serial� Write� Operations�

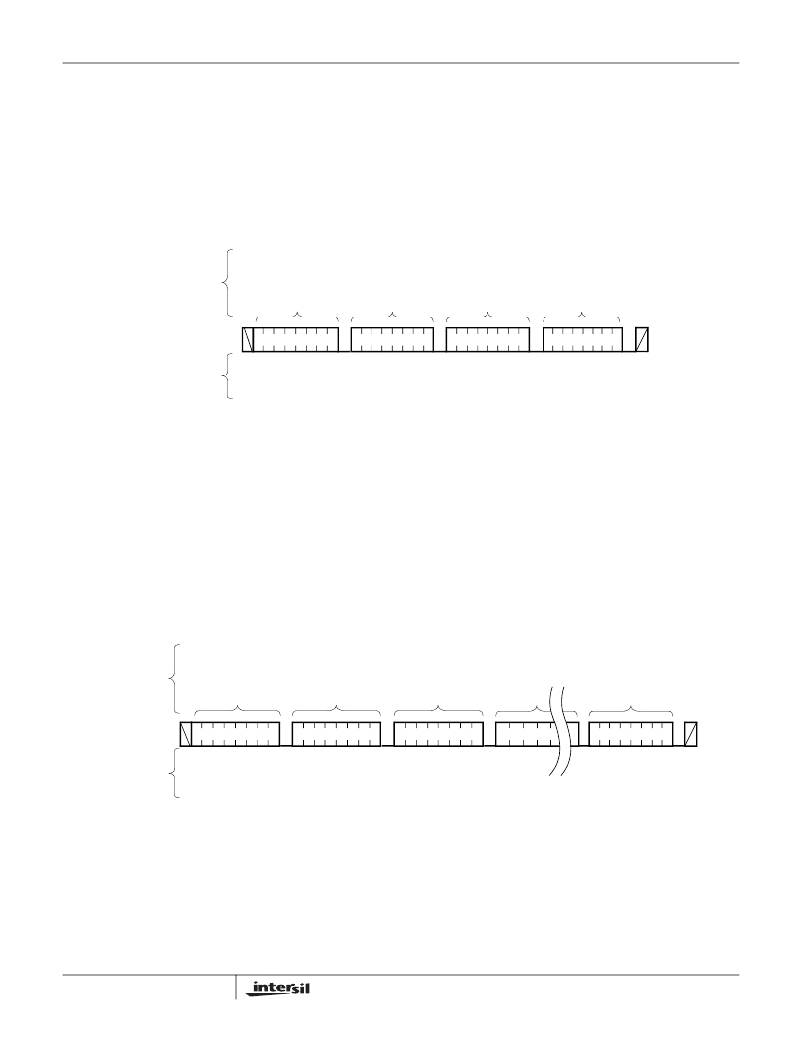

�B� YTE� W� RITE�

�For� a� write� operation,� the� device� requires� the� Slave�

�Address� Byte� and� a� Word� Address� Byte.� This� gives� the�

�master� access� to� any� one� of� the� words� in� the� array.�

�After� receipt� of� the� Word� Address� Byte,� the� device�

�responds� with� an� acknowledge,� and� awaits� the� next�

�Figure� 8.� Byte� Write� Sequence�

�eight� bits� of� data.� After� receiving� the� 8-bits� of� the� Data�

�Byte,� the� device� again� responds� with� an� acknowledge.�

�The� master� then� terminates� the� transfer� by� generating� a�

�stop� condition,� at� which� time� the� device� begins� the� inter-�

�nal� write� cycle� to� the� nonvolatile� memory.� During� this�

�internal� write� cycle,� the� device� inputs� are� disabled,� so� the�

�device� will� not� respond� to� any� requests� from� the� master.�

�The� SDA� output� is� at� high� impedance.� See� Figure� 8.�

�Signals� from�

�the� Master�

�S�

�t�

�a�

�r�

�t�

�Slave�

�Address�

�Word� Address�

�Byte� 1�

�Word� Address�

�Byte� 0�

�Data�

�S�

�t�

�o�

�p�

�SDA� Bus�

�1� 0� 1� 0�

�0�

�Signals� from�

�the� Slave�

�A�

�C�

�K�

�A�

�C�

�K�

�A�

�C�

�K�

�A�

�C�

�K�

�A� write� to� a� protected� block� of� memory� will� suppress� the� acknowledge� bit.�

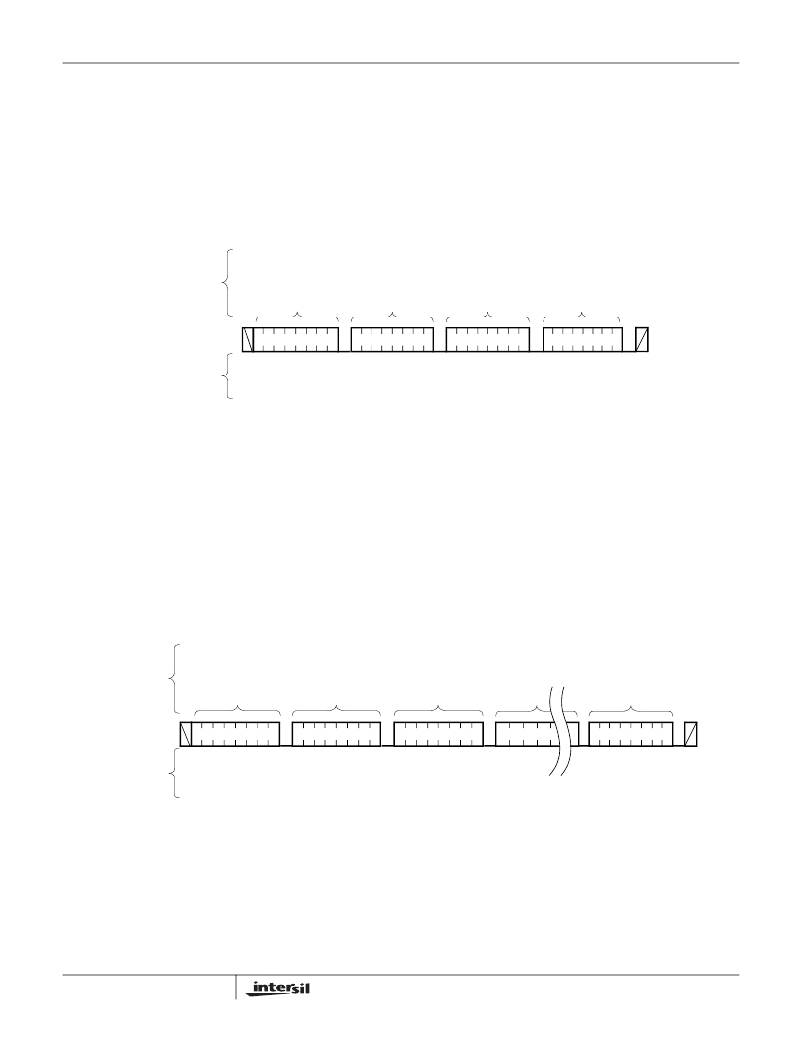

�Page� Write�

�The� device� is� capable� of� a� page� write� operation.� It� is�

�initiated� in� the� same� manner� as� the� byte� write� opera-�

�tion;� but� instead� of� terminating� the� write� cycle� after� the�

�first� data� byte� is� transferred,� the� master� can� transmit�

�an� unlimited� number� of� 8-bit� bytes.� After� the� receipt� of�

�each� byte,� the� device� will� respond� with� an� acknowl-�

�edge,� and� the� address� is� internally� incremented� by�

�one.� The� page� address� remains� constant.� When� the�

�counter� reaches� the� end� of� the� page,� it� “rolls� over”� and�

�Figure� 9.� Page� Write� Operation�

�goes� back� to� ‘0’� on� the� same� page.� This� means� that�

�the� master� can� write� 64-bytes� to� the� page� starting� at�

�any� location� on� that� page.� If� the� master� begins� writing�

�at� location� 60,� and� loads� 12-bytes,� then� the� first� 4-�

�bytes� are� written� to� locations� 60� through� 63,� and� the�

�last� 8-bytes� are� written� to� locations� 0� through� 7.� After-�

�wards,� the� address� counter� would� point� to� location� 8� of�

�the� page� that� was� just� written.� If� the� master� supplies�

�more� than� 64-bytes� of� data,� then� new� data� over-writes�

�the� previous� data,� one� byte� at� a� time.�

�Signals� from�

�the� Master�

�S�

�t�

�a�

�r�

�t�

�Slave�

�Address�

�Word� Address�

�Byte� 1�

�Word� Address�

�Byte� 0�

�Data�

�(1)�

�(1� ≤� n� ≤� 64)�

�Data�

�(n)�

�S�

�t�

�o�

�p�

�SDA� Bus�

�1� 0� 1� 0�

�0�

�Signals� from�

�the� Slave�

�A�

�C�

�K�

�A�

�C�

�K�

�A�

�C�

�K�

�A�

�C�

�K�

�A�

�C�

�K�

�11�

�FN8122.1�

�May� 25,� 2006�

�相关PDF资料 |

PDF描述 |

|---|---|

| GMM31DTBT-S189 | CONN EDGECARD 62POS R/A .156 SLD |

| ABC10DRAH-S734 | CONN EDGECARD 20POS .100 R/A PCB |

| GSM31DTAT-S189 | CONN EDGECARD 62POS R/A .156 SLD |

| CS5157HGDR16 | IC CTRLR BUCK SYNC 5BIT 16SOIC |

| X4323V8I-2.7A | IC SUPERVISOR CPU 32K EE 8-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X4323V8IZ | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 32k EEPROM |

| X4323V8IZ-2.7 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 32k EEPROM |

| X4323V8IZ-2.7A | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 32k EEPROM |

| X4323V8Z | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 32k EEPROM |

| X4323V8Z-2.7 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 32k EEPROM |

发布紧急采购,3分钟左右您将得到回复。