- 您现在的位置:买卖IC网 > PDF目录15088 > X5043S8Z-4.5A (Intersil)IC CPU SUPERV 4K EEPROM 8-SOIC PDF资料下载

参数资料

| 型号: | X5043S8Z-4.5A |

| 厂商: | Intersil |

| 文件页数: | 6/21页 |

| 文件大小: | 0K |

| 描述: | IC CPU SUPERV 4K EEPROM 8-SOIC |

| 标准包装: | 100 |

| 类型: | 简单复位/加电复位 |

| 监视电压数目: | 1 |

| 输出: | 开路漏极或开路集电极 |

| 复位: | 低有效 |

| 复位超时: | 最小为 100 ms |

| 电压 - 阀值: | 4.62V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-SOIC(0.154",3.90mm 宽) |

| 供应商设备封装: | 8-SOIC |

| 包装: | 管件 |

�� �

�

�

�X5043,� X5045�

�no� microprocessor� action,� the� watchdog� timer� control� bits�

�remain� unchanged,� even� during� total� power� failure.�

�V� CC� Threshold� Reset� Procedure�

�The� X5043,� X5045� are� shipped� with� a� standard� V� CC�

�threshold� (V� TRIP� )� voltage.� This� value� will� not� change� over�

�normal� operating� and� storage� conditions.� However,� in�

�applications� where� the� standard� V� TRIP� is� not� exactly� right,� or�

�if� higher� precision� is� needed� in� the� V� TRIP� value,� the� X5043,�

�X5045� threshold� may� be� adjusted.� The� procedure� is�

�described� below,� and� uses� the� application� of� a� high� voltage�

�control� signal.�

�Setting� the� V� TRIP� Voltage�

�This� procedure� is� used� to� set� the� V� TRIP� to� a� higher� voltage�

�value.� For� example,� if� the� current� V� TRIP� is� 4.4V� and� the� new�

�V� TRIP� is� 4.6V,� this� procedure� will� directly� make� the� change.� If�

�the� new� setting� is� to� be� lower� than� the� current� setting,� then� it�

�is� necessary� to� reset� the� trip� point� before� setting� the� new�

�value.�

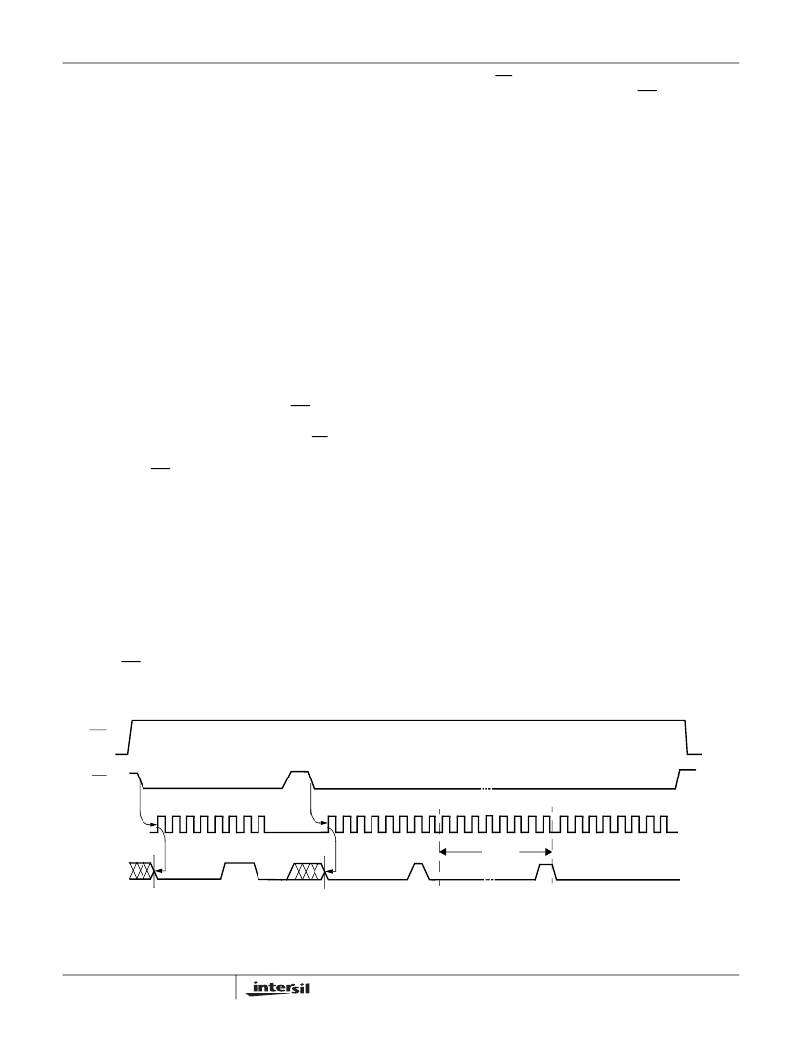

�To� set� the� new� V� TRIP� voltage,� apply� the� desired� V� TRIP�

�threshold� voltage� to� the� V� CC� pin� and� tie� the� WP� pin� to� the�

�programming� voltage� V� P� .� Then� send� a� WREN� command,�

�followed� by� a� write� of� Data� 00h� to� address� 01h.� CS� going�

�HIGH� on� the� write� operation� initiates� the� V� TRIP� programming�

�sequence.� Bring� WP� LOW� to� complete� the� operation.�

�Note:� This� operation� also� writes� 00h� to� array� address� 01h.�

�Resetting� the� V� TRIP� Voltage�

�This� procedure� is� used� to� set� the� V� TRIP� to� a� “native”� voltage�

�level.� For� example,� if� the� current� V� TRIP� is� 4.4V� and� the� new�

�V� TRIP� must� be� 4.0V,� then� the� V� TRIP� must� be� reset.� When�

�V� TRIP� is� reset,� the� new� V� TRIP� is� something� less� than� 1.7V.�

�This� procedure� must� be� used� to� set� the� voltage� to� a� lower�

�value.�

�To� reset� the� V� TRIP� voltage,� apply� at� least� 3V� to� the� V� CC� pin�

�and� tie� the� WP� pin� to� the� programming� voltage� V� P� .� Then�

�send� a� WREN� command,� followed� by� a� write� of� Data� 00h� to�

�address� 03h.� CS� going� HIGH� on� the� write� operation� initiates�

�the� V� TRIP� programming� sequence.� Bring� WP� LOW� to�

�complete� the� operation.�

�Note:� This� operation� also� writes� 00h� to� array� address� 03h.�

�WP�

�CS�

�0� 1� 2� 3� 4� 5� 6� 7�

�V� P� =� 15-18V�

�0 1 2 3 4 5 6 7 8 9� 10� 11� 12� 13� 14� 15�

�SCK�

�8� Bits�

�SI�

�06h�

�WREN�

�02h�

�Write�

�01h�

�Address�

�00h�

�Data�

�FIGURE� 1.� SET� V� TRIP� LEVEL� SEQUENCE� (V� CC� =� DESIRED� V� TRIP� VALUE.)�

�6�

�FN8126.2�

�March� 16,� 2006�

�相关PDF资料 |

PDF描述 |

|---|---|

| GMM18DRTI-S13 | CONN EDGECARD 36POS .156 EXTEND |

| X4045S8Z-2.7A | IC CPU SUPERV 4K EEPROM 8-SOIC |

| RBM36DSEI | CONN EDGECARD 72POS .156 EYELET |

| H2AXG-10108-V4-ND | JUMPER-H1503TR/A2015V/X 8" |

| H2AXG-10108-S4-ND | JUMPER-H1503TR/A2015S/X 8" |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X5043S8ZT1 | 功能描述:IC SUPERVISOR CPU 4K EE 8-SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极或开路集电极 复位:低有效 复位超时:最小为 600 ms 电压 - 阀值:3.8V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:SC-74A,SOT-753 供应商设备封装:SOT-23-5 包装:带卷 (TR) |

| X5043SM | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 4K SPI EEPROM |

| X5043ST1 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 4K SPI EEPROM |

| X5043ST2 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 4K SPI EEPROM |

| X5043V | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:CPU Supervisor with 4K SPI EEPROM |

发布紧急采购,3分钟左右您将得到回复。