- 您现在的位置:买卖IC网 > PDF目录15063 > X5045M8IZ-2.7A (Intersil)IC CPU SUPERV 4K EEPROM 8-MSOP PDF资料下载

参数资料

| 型号: | X5045M8IZ-2.7A |

| 厂商: | Intersil |

| 文件页数: | 5/21页 |

| 文件大小: | 0K |

| 描述: | IC CPU SUPERV 4K EEPROM 8-MSOP |

| 标准包装: | 80 |

| 类型: | 简单复位/加电复位 |

| 监视电压数目: | 1 |

| 输出: | 开路漏极或开路集电极 |

| 复位: | 高有效 |

| 复位超时: | 最小为 100 ms |

| 电压 - 阀值: | 2.92V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-TSSOP,8-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 8-MSOP |

| 包装: | 管件 |

�� �

�

�

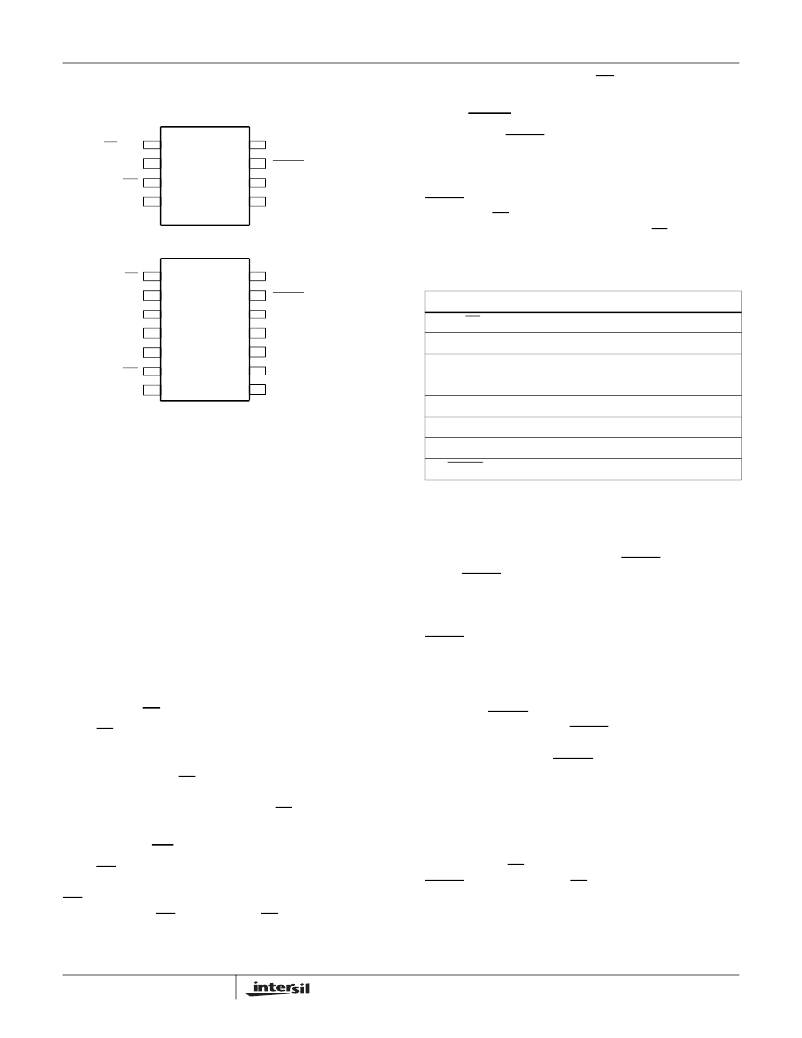

�X5043,� X5045�

�Pin� Configuration�

�8� Ld� SOIC/PDIP/MSOP�

�cycle� has� already� been� initiated,� WP� going� low� will� have� no�

�affect� on� a� write.�

�Reset� (RESET,� RESET)�

�CS/WDI�

�SO�

�WP�

�V� SS�

�1�

�2�

�3�

�4�

�8�

�7�

�X5043,� X5045�

�6�

�5�

�V� CC�

�RESET/RESET�

�SCK�

�SI�

�X5043,� X5045,� RESET/RESET� is� an� active� low/HIGH,� open�

�drain� output� which� goes� active� whenever� V� CC� falls� below� the�

�minimum� V� CC� sense� level.� It� will� remain� active� until� V� CC�

�rises� above� the� minimum� V� CC� sense� level� for� 200ms.�

�RESET/RESET� also� goes� active� if� the� Watchdog� timer� is�

�enabled� and� CS� remains� either� high� or� low� longer� than� the�

�Watchdog� time� out� period.� A� falling� edge� of� CS� will� reset� the�

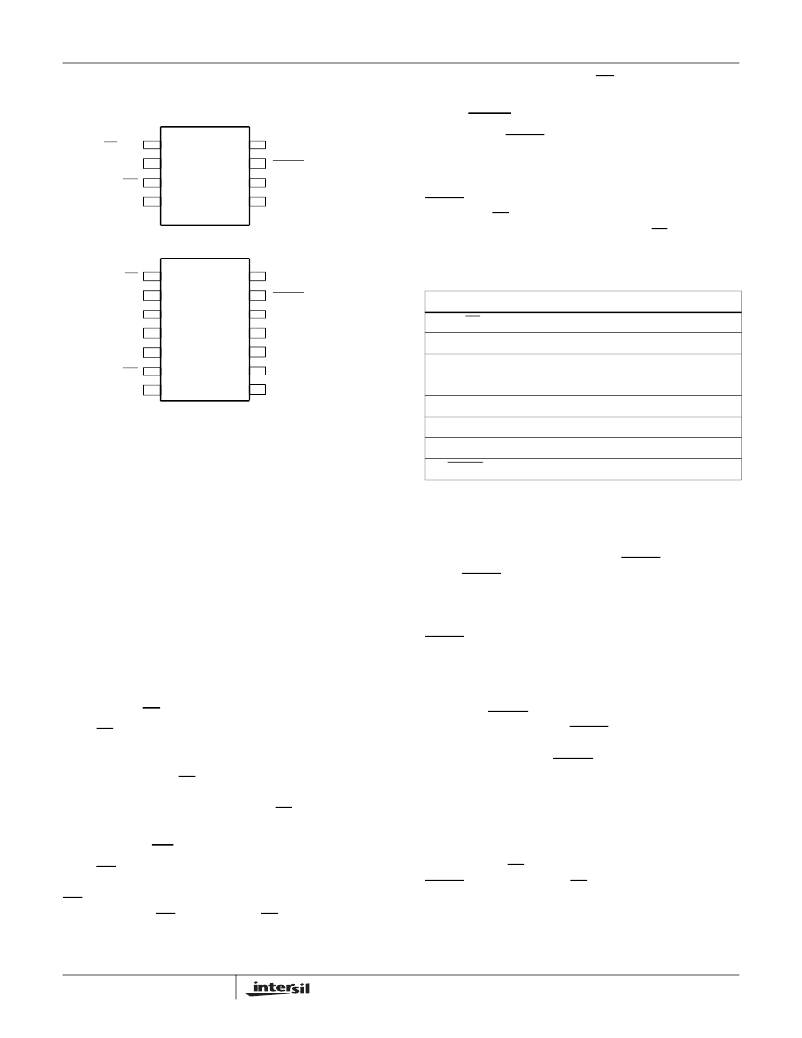

�14� Ld� TSSOP�

�watchdog� timer.�

�CS�

�1�

�14�

�V� CC�

�Pin� Names�

�SO�

�NC�

�NC�

�NC�

�WP�

�V� SS�

�2�

�3�

�4�

�5�

�6�

�7�

�13�

�12�

�X5043,� X5045�

�11�

�10�

�9�

�8�

�RESET/RESET�

�NC�

�NC�

�NC�

�SCK�

�SI�

�SYMBOL�

�CS/WDI�

�SO�

�SI�

�SCK�

�DESCRIPTION�

�Chip� Select� Input�

�Serial� Output�

�Serial� Input�

�Serial� Clock� Input�

�WP�

�Write� Protect� Input�

�Pin� Descriptions�

�Serial� Output� (SO)�

�SO� is� a� push/pull� serial� data� output� pin.� During� a� read� cycle,�

�V� SS�

�V� CC�

�RESET/RESET�

�Ground�

�Supply� Voltage�

�Reset� Output�

�data� is� shifted� out� on� this� pin.� Data� is� clocked� out� by� the�

�falling� edge� of� the� serial� clock.�

�Serial� Input� (SI)�

�SI� is� the� serial� data� input� pin.� All� opcodes,� byte� addresses,�

�and� data� to� be� written� to� the� memory� are� input� on� this� pin.�

�Data� is� latched� by� the� rising� edge� of� the� serial� clock.�

�Serial� Clock� (SCK)�

�The� Serial� Clock� controls� the� serial� bus� timing� for� data� input�

�and� output.� Opcodes,� addresses,� or� data� present� on� the� SI�

�pin� is� latched� on� the� rising� edge� of� the� clock� input,� while� data�

�on� the� SO� pin� changes� after� the� falling� edge� of� the� clock�

�input.�

�Chip� Select� (CS/WDI)�

�When� CS� is� high,� the� X5043,� X5045� are� deselected� and� the�

�SO� output� pin� is� at� high� impedance� and,� unless� an� internal�

�write� operation� is� underway,� the� X5043,� X5045� will� be� in� the�

�standby� power� mode.� CS� low� enables� the� X5043,� X5045,�

�placing� it� in� the� active� power� mode.� It� should� be� noted� that�

�after� power-up,� a� high� to� low� transition� on� CS� is� required� prior�

�to� the� start� of� any� operation.�

�Write� Protect� (WP)�

�When� WP� is� low,� nonvolatile� writes� to� the� X5043,� X5045� are�

�disabled,� but� the� part� otherwise� functions� normally.� When�

�WP� is� held� high,� all� functions,� including� non� volatile� writes�

�operate� normally.� WP� going� low� while� CS� is� still� low� will�

�interrupt� a� write� to� the� X5043,� X5045.� If� the� internal� write�

�5�

�Principles� of� Operation�

�Power-on� Reset�

�Application� of� power� to� the� X5043,� X5045� activate� a� Power-�

�on� Reset� Circuit.� This� circuit� pulls� the� RESET/RESET� pin�

�active.� RESET/RESET� prevents� the� system� microprocessor�

�from� starting� to� operate� with� insufficient� voltage� or� prior� to�

�stabilization� of� the� oscillator.� When� V� CC� exceeds� the� device�

�V� TRIP� value� for� 200ms� (nominal)� the� circuit� releases�

�RESET/RESET,� allowing� the� processor� to� begin� executing�

�code.�

�Low� Voltage� Monitoring�

�During� operation,� the� X5043,� X5045� monitor� the� V� CC� level�

�and� asserts� RESET/RESET� if� supply� voltage� falls� below� a�

�preset� minimum� V� TRIP� .� The� RESET/RESET� signal� prevents�

�the� microprocessor� from� operating� in� a� power� fail� or�

�brownout� condition.� The� RESET/RESET� signal� remains�

�active� until� the� voltage� drops� below� 1V.� It� also� remains� active�

�until� V� CC� returns� and� exceeds� V� TRIP� for� 200ms.�

�Watchdog� Timer�

�The� Watchdog� Timer� circuit� monitors� the� microprocessor�

�activity� by� monitoring� the� WDI� input.� The� microprocessor�

�must� toggle� the� CS/WDI� pin� periodically� to� prevent� an� active�

�RESET/RESET� signal.� The� CS/WDI� pin� must� be� toggled�

�from� HIGH� to� LOW� prior� to� the� expiration� of� the� watchdog�

�time� out� period.� The� state� of� two� nonvolatile� control� bits� in�

�the� Status� Register� determines� the� watchdog� timer� period.�

�The� microprocessor� can� change� these� watchdog� bits.� With�

�FN8126.2�

�March� 16,� 2006�

�相关PDF资料 |

PDF描述 |

|---|---|

| X5045M8IZ-2.7 | IC CPU SUPERV 4K EE RST 8-MSOP |

| VI-B4T-EV-F3 | CONVERTER MOD DC/DC 6.5V 150W |

| X5045M8IZ-4.5A | IC CPU SUPERV 4K EEPROM 8-MSOP |

| X4045M8IZ-2.7A | IC CPU SUPERV 4K EEPROM 8-MSOP |

| ISL6564CR | IC REG CTRLR BUCK PWM VM 40-QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X5045M8IZ-4.5A | 功能描述:IC CPU SUPERV 4K EEPROM 8-MSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极或开路集电极 复位:低有效 复位超时:最小为 600 ms 电压 - 阀值:3.8V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:SC-74A,SOT-753 供应商设备封装:SOT-23-5 包装:带卷 (TR) |

| X5045M8Z | 功能描述:IC CPU SUPERV 4K EE RST 8-MSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极或开路集电极 复位:低有效 复位超时:最小为 600 ms 电压 - 阀值:3.8V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:SC-74A,SOT-753 供应商设备封装:SOT-23-5 包装:带卷 (TR) |

| X5045M8Z-2.7 | 功能描述:IC CPU SUPERV 4K EE RST 8-MSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极或开路集电极 复位:低有效 复位超时:最小为 600 ms 电压 - 阀值:3.8V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:SC-74A,SOT-753 供应商设备封装:SOT-23-5 包装:带卷 (TR) |

| X5045M8Z-2.7A | 功能描述:IC CPU SUPERV 4K EEPROM 8-MSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极或开路集电极 复位:低有效 复位超时:最小为 600 ms 电压 - 阀值:3.8V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:SC-74A,SOT-753 供应商设备封装:SOT-23-5 包装:带卷 (TR) |

| X5045M8Z-4.5A | 功能描述:IC CPU SUPERV 4K EEPROM 8-MSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:开路漏极或开路集电极 复位:低有效 复位超时:最小为 600 ms 电压 - 阀值:3.8V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:SC-74A,SOT-753 供应商设备封装:SOT-23-5 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。