参数资料

| 型号: | X5648PI |

| 厂商: | Intersil |

| 文件页数: | 6/18页 |

| 文件大小: | 0K |

| 描述: | IC SUPERVISOR CPU 64K EE 8-DIP |

| 标准包装: | 50 |

| 类型: | 简单复位/加电复位 |

| 监视电压数目: | 1 |

| 输出: | 开路漏极或开路集电极 |

| 复位: | 低有效 |

| 复位超时: | 最小为 100 ms |

| 电压 - 阀值: | 4.38V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 8-DIP(0.300",7.62mm) |

| 供应商设备封装: | 8-PDIP |

| 包装: | 管件 |

�� �

�

�

�X5648,� X5649�

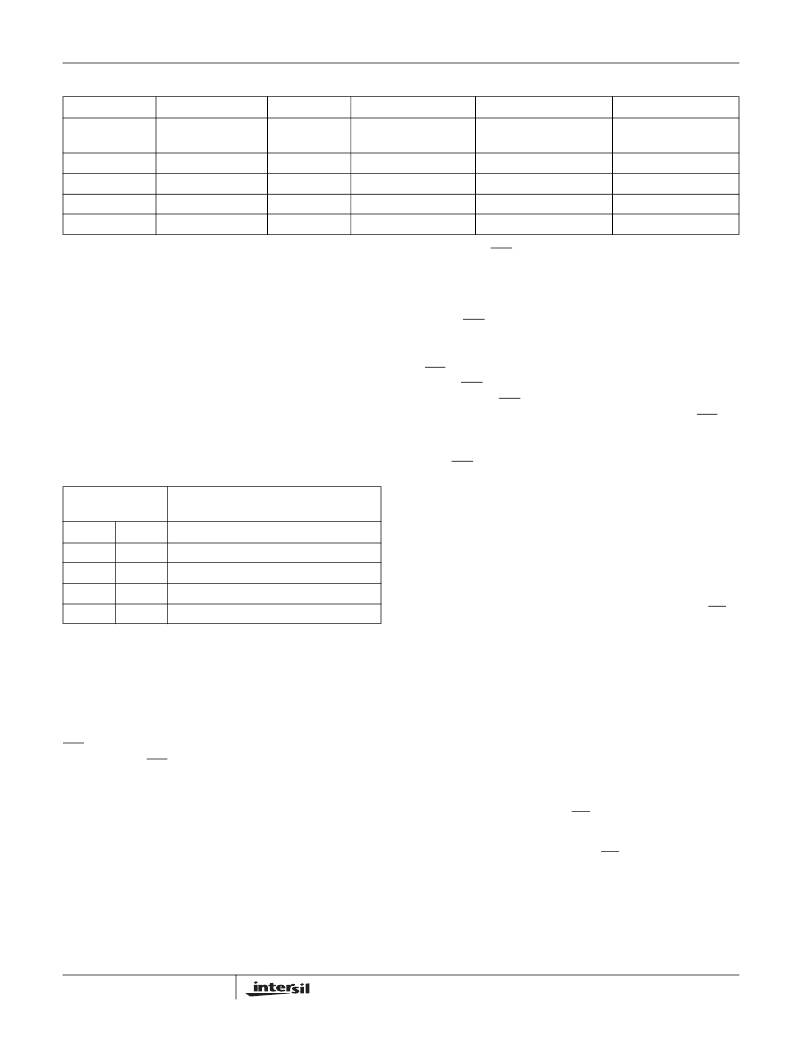

�Table� 2.� Block� Protect� Matrix�

�WREN� CMD�

�Status� Register�

�Device� Pin�

�Block�

�Block�

�Status� Register�

�WPEN,� BL0,� BL1�

�WEL�

�0�

�1�

�1�

�1�

�WPEN�

�X�

�1�

�0�

�X�

�WP#�

�X�

�0�

�X�

�1�

�Protected� Block�

�Protected�

�Protected�

�Protected�

�Protected�

�Unprotected� Block�

�Protected�

�Writable�

�Writable�

�Writable�

�WD0,� WD1�

�Protected�

�Protected�

�Writable�

�Writable�

�The� Write� Enable� Latch� (WEL)� bit� indicates� the� sta-�

�tus� of� the� write� enable� latch.� When� WEL� =� 1,� the�

�latch� is� set� HIGH� and� when� WEL� =� 0� the� latch� is� reset�

�LOW.� The� WEL� bit� is� a� volatile,� read� only� bit.� It� can�

�be� set� by� the� WREN� instruction� and� can� be� reset� by�

�the� WRDS� instruction.�

�The� block� lock� bits,� BL0� and� BL1,� set� the� level� of� block�

�lock� protection.� These� nonvolatile� bits� are� pro-�

�grammed� using� the� WRSR� instruction� and� allow� the�

�user� to� protect� one� quarter,� one� half,� all� or� none� of� the�

�EEPROM� array.� Any� portion� of� the� array� that� is� block�

�lock� protected� can� be� read� but� not� written.� It� will�

�remain� protected� until� the� BL� bits� are� altered� to� disable�

�block� lock� protection� of� that� portion� of� memory.�

�Setting� the� WP� pin� LOW� while� WPEN� is� a� “1”� while� an�

�internal� write� cycle� to� the� status� register� is� in� progress�

�will� not� stop� this� write� operation,� but� the� operation� dis-�

�ables� subsequent� write� attempts� to� the� status� register.�

�When� WP� is� HIGH,� all� functions,� including� nonvolatile�

�writes� to� the� status� register� operate� normally.� Setting�

�the� WPEN� bit� in� the� status� register� to� “0”� blocks� the�

�WP� pin� function,� allowing� writes� to� the� status� register�

�when� WP� is� HIGH� or� LOW.� Setting� the� WPEN� bit� to�

�“1”� while� the� WP� pin� is� LOW� activates� the� programma-�

�ble� ROM� mode,� thus� requiring� a� change� in� the� WP� pin�

�prior� to� subsequent� status� register� changes.� This�

�allows� manufacturing� to� install� the� device� in� a� system�

�with� WP� pin� grounded� and� still� be� able� to� program� the�

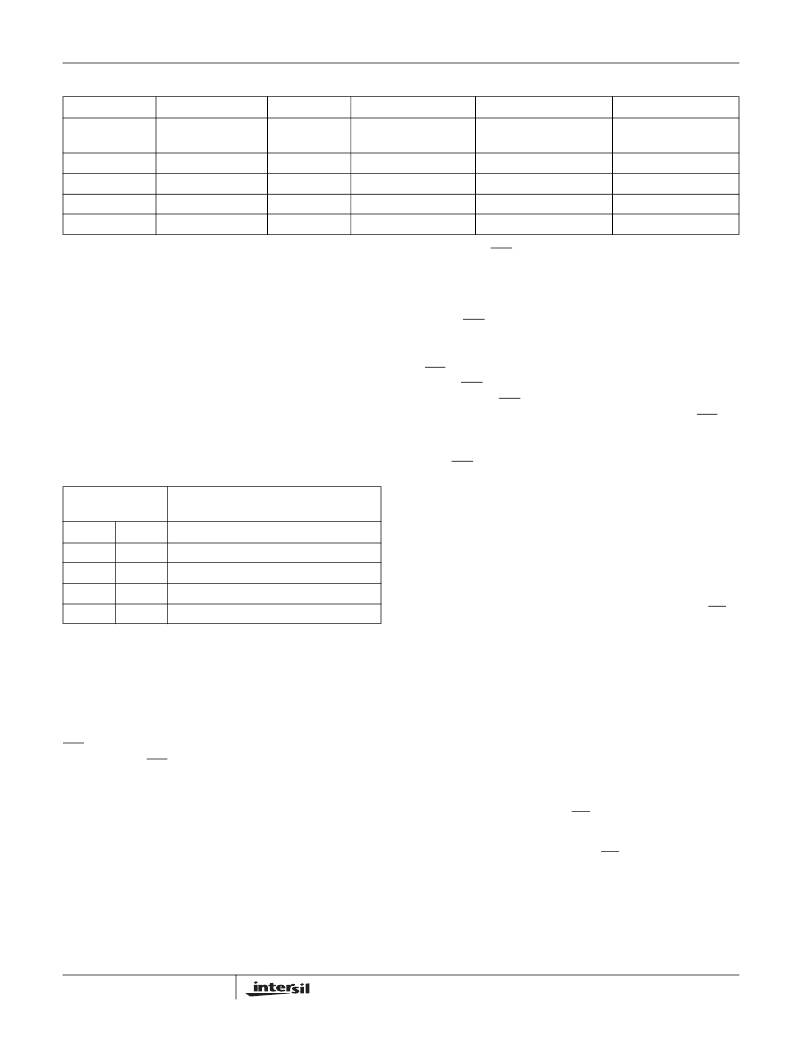

�Status�

�Register� Bits�

�Array� Addresses� Protected�

�status� register.� Manufacturing� can� then� load� configura-�

�tion� data,� manufacturing� time� and� other� parameters�

�into� the� EEPROM,� then� set� the� portion� of� memory� to�

�BL1�

�0�

�0�

�1�

�1�

�BL0�

�0�

�1�

�0�

�1�

�X5648/X5649�

�None�

�$1800-$1FFF�

�$1000-$1FFF�

�$0000-$1FFF�

�be� protected� by� setting� the� block� lock� bits,� and� finally�

�set� the� “OTP� mode”� by� setting� the� WPEN� bit.� Data�

�changes� now� require� a� hardware� change.�

�Read� Sequence�

�When� reading� from� the� EEPROM� memory� array,� CS� is�

�first� pulled� low� to� select� the� device.� The� 8-bit� READ�

�The� FLAG� bit� shows� the� status� of� a� volatile� latch� that�

�can� be� set� and� reset� by� the� system� using� the� SFLB�

�and� RFLB� instructions.� The� flag� bit� is� automatically�

�reset� upon� power-up.�

�The� nonvolatile� WPEN� bit� is� programmed� using� the�

�WRSR� instruction.� This� bit� works� in� conjunction� with� the�

�WP� pin� to� provide� an� in-circuit� programmable� ROM� func-�

�tion� (Table� 2).� WP� is� LOW� and� WPEN� bit� programmed�

�HIGH� disables� all� status� register� write� operations.�

�In� Circuit� Programmable� ROM� Mode�

�This� mechanism� protects� the� block� lock� and� watchdog�

�bits� from� inadvertent� corruption.�

�In� the� locked� state� (programmable� ROM� Mode)� the�

�WP� pin� is� LOW� and� the� nonvolatile� bit� WPEN� is� “1”.�

�This� mode� disables� nonvolatile� writes� to� the� device’s�

�status� register.�

�6�

�instruction� is� transmitted� to� the� device,� followed� by� the�

�16-bit� address.� After� the� READ� opcode� and� address�

�are� sent,� the� data� stored� in� the� memory� at� the� selected�

�address� is� shifted� out� on� the� SO� line.� The� data� stored�

�in� memory� at� the� next� address� can� be� read� sequen-�

�tially� by� continuing� to� provide� clock� pulses.� The�

�address� is� automatically� incremented� to� the� next�

�higher� address� after� each� byte� of� data� is� shifted� out.�

�When� the� highest� address� is� reached,� the� address�

�counter� rolls� over� to� address� $0000� allowing� the� read�

�cycle� to� be� continued� indefinitely.� The� read� operation�

�is� terminated� by� taking� CS� high.� Refer� to� the� read�

�EEPROM� array� sequence� (Figure� 1).�

�To� read� the� status� register,� the� CS� line� is� first� pulled� low�

�to� select� the� device� followed� by� the� 8-bit� RDSR� instruc-�

�tion.� After� the� RDSR� opcode� is� sent,� the� contents� of� the�

�status� register� are� shifted� out� on� the� SO� line.� Refer� to�

�the� read� status� register� sequence� (Figure� 2).�

�FN8136.0�

�March� 17,� 2005�

�相关PDF资料 |

PDF描述 |

|---|---|

| X5648P-4.5A | IC SUPERVISOR CPU 64K EE 8-DIP |

| MAX8805XEWEBD+T | IC PWM STEP-DN CONV 650MA 16-WLP |

| GCM43DTBI-S189 | CONN EDGECARD 86POS R/A .156 SLD |

| MAX8805XEWEEE+T | IC PWM STEP-DN CONV 650MA 16-WLP |

| AYM10DRMD | CONN EDGECARD 20POS .156 WW |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X5648PI-2.7 | 功能描述:IC SUPERVISOR CPU 64K EE 8-DIP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:推挽式,图腾柱 复位:低有效 复位超时:最小 145 ms 电压 - 阀值:2.64V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-WQFN 裸露焊盘 供应商设备封装:16-TQFN-EP(4x4) 包装:带卷 (TR) |

| X5648PI-2.7A | 功能描述:IC SUPERVISOR CPU 64K EE 8-DIP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:推挽式,图腾柱 复位:低有效 复位超时:最小 145 ms 电压 - 阀值:2.64V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-WQFN 裸露焊盘 供应商设备封装:16-TQFN-EP(4x4) 包装:带卷 (TR) |

| X5648PI-4.5A | 功能描述:IC SUPERVISOR CPU 64K EE 8-DIP RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:推挽式,图腾柱 复位:低有效 复位超时:最小 145 ms 电压 - 阀值:2.64V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-WQFN 裸露焊盘 供应商设备封装:16-TQFN-EP(4x4) 包装:带卷 (TR) |

| X5648S14 | 功能描述:IC SUPERVISOR CPU 64K EE 14-SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 监控器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:简单复位/加电复位 监视电压数目:1 输出:推挽式,图腾柱 复位:低有效 复位超时:最小 145 ms 电压 - 阀值:2.64V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-WQFN 裸露焊盘 供应商设备封装:16-TQFN-EP(4x4) 包装:带卷 (TR) |

| X5648S14-1.8 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:SPI Serial EEPROM with Supervisory Features |

发布紧急采购,3分钟左右您将得到回复。