- 您现在的位置:买卖IC网 > PDF目录376449 > X98024L128-3.3-Z (INTERSIL CORP) 240MHz Triple Video Digitizer with Digital PLL PDF资料下载

参数资料

| 型号: | X98024L128-3.3-Z |

| 厂商: | INTERSIL CORP |

| 元件分类: | 消费家电 |

| 英文描述: | 240MHz Triple Video Digitizer with Digital PLL |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP128 |

| 封装: | 14 X 20 MM, ROHS COMPLIANT, MS-022, MQFP-128 |

| 文件页数: | 22/29页 |

| 文件大小: | 295K |

| 代理商: | X98024L128-3.3-Z |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页

22

FN8220.0

June 6, 2005

HSYNC

OUT

HSYNC

OUT

is an unmodified, buffered version of the

incoming HSYNC

IN

or SOG

IN

signal of the selected

channel, with the incoming signal’s period, polarity, and

width to aid in mode detection. HSYNC

OUT

will be the same

format as the incoming sync signal: either horizontal or

composite sync. If a SOG input is selected, HSYNC

OUT

will

output the entire SOG signal, including the VSYNC portion,

pre-/post-equalization pulses if present, and Macrovision

pulses if present. HSYNC

OUT

remains active when the

X98024 is in power-down mode. HSYNC

OUT

is generally

used for mode detection.

VSYNC

OUT

VSYNC

OUT

is an unmodified, buffered version of the

incoming VSYNC

IN

signal of the selected channel, with the

original VSYNC period, polarity, and width to aid in mode

detection. If a SOG input is selected, this signal will output

the VSYNC signal extracted by the X98024’s sync slicer.

Extracted VSYNC will be the width of the embedded VSYNC

pulse plus pre- and post-equalization pulses (if present).

Macrovision pulses from an NTSC DVD source will lengthen

the width of the VSYNC pulse. Macrovision pulses from

other sources (PAL DVD or videotape) may appear as a

second VSYNC pulse encompassing the width of the

Macrovision. See the Macrovision section for more

information. VSYNC

OUT

(including the sync separator

function) remains active in power-down mode. VSYNC

OUT

is generally used for mode detection, start of field detection,

and even/odd field detection.

HS

OUT

HS

OUT

is generated by the X98024’s control logic and is

synchronized to the output DATACLK and the digital pixel

data on the output databus. Its trailing edge is aligned with

pixel 0. Its width, in units of pixels, is determined by register

0x19, and its polarity is determined by register 0x18[7]. As

the width is increased, the trailing edge stays aligned with

pixel 0, while the leading edge is moved backwards in time

relative to pixel 0. HS

OUT

is used by the scaler to signal the

start of a new line of pixels.

The HSOUT Width register (0x19) controls the width of the

HS

OUT

pulse. The pulse width is nominally 1 pixel clock

period times the value in this register. In the 48 bit output

mode (register 0x18[0] = 1), or the YUV input mode (register

0x05[2] = 1), the HS

OUT

width is incremented in 2 pixel clock

(1 DATACLK) increments (see Table 7).

VS

OUT

VS

OUT

is generated by the X98024’s control logic and is

synchronized to the output DATACLK and the digital pixel

data on the output databus. Its leading and trailing edges are

aligned with pixel 7 (8 pixels after HSYNC trailing edge). Its

width, in units of lines, is equal to the width of the incoming

VSYNC (see the VSYNC

OUT

description). Its polarity is

determined by register 0x18[6].

This output is not needed in

most applications.

Macrovision

The X98024 will synchronize to and digitize Macrovision-

encoded YUV video if the source is an NTSC DVD.

Macrovision from PAL DVD, or from all video tape sources,

is incompatible with the sync slicer, requiring that the

Macrovision pulses either be stripped from the video prior to

the SOG

IN

input, or an external COAST signal be generated

and applied to the CLKINV pin that will coast the X98024’s

PLL during the VSYNC and Macrovision period.

Standby Mode

The X98024 can be placed into a low power standby mode

by writing a 0x0F to register 0x1B, powering down the triple

ADCs, the DPLL, and most of the internal clocks.

To allow input monitoring and mode detection during power-

down, the following blocks remain active:

Serial interface (including the crystal oscillator) to enable

register read/write activity

Activity and polarity detect functions (registers 0x01 and

0x02)

The HSYNC

OUT

and VSYNC

OUT

pins (for mode

detection)

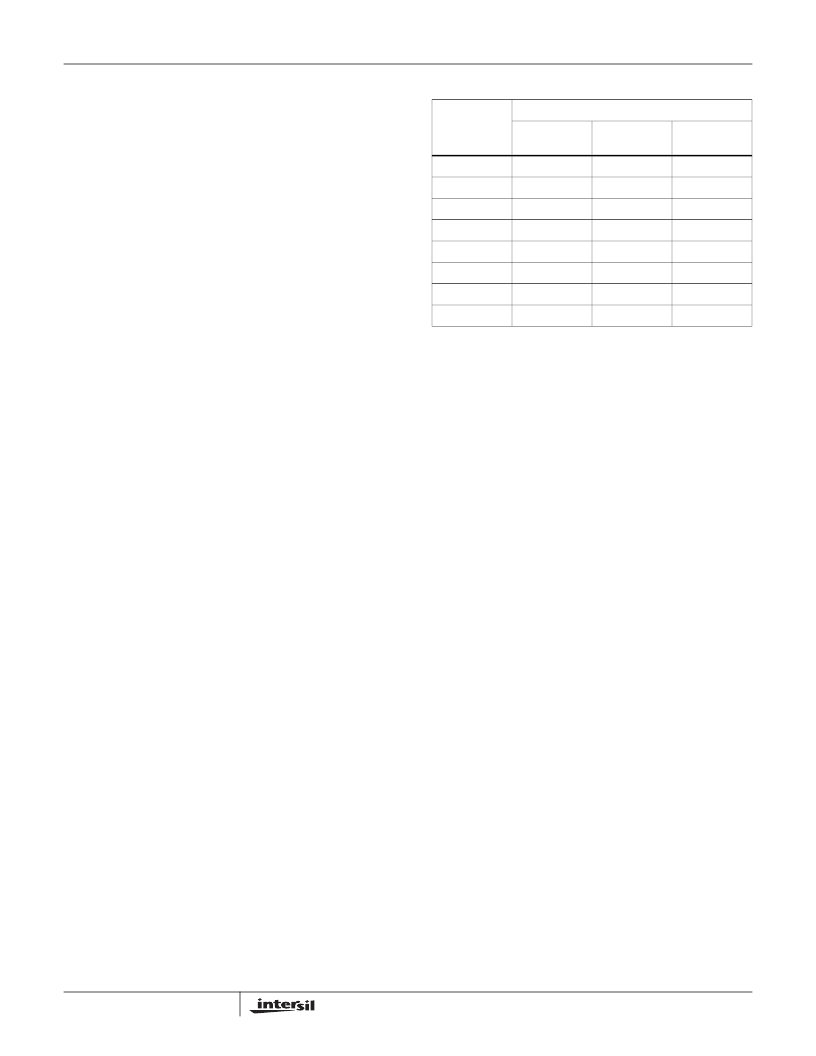

TABLE 7. HS

OUT

WIDTH

REGISTER

0x19 VALUE

HS

OUT

WIDTH (PIXEL CLOCKS)

24 BIT MODE,

RGB

24 BIT MODE,

YUV

ALL 48 BIT

MODES

0

0

1

0

1

1

1

0

2

2

3

2

3

3

3

2

4

4

5

4

5

5

5

4

6

6

7

6

7

7

7

6

X98024

相关PDF资料 |

PDF描述 |

|---|---|

| XC145481 | 3 V PCM Codec-Filter |

| XC145481DW | 3 V PCM Codec-Filter |

| XC145481P | 3 V PCM Codec-Filter |

| XC145481SD | 3 V PCM Codec-Filter |

| XCWB201 | Silver Mica Capacitor; Capacitance:470pF; Capacitance Tolerance:+/- 2%; Series:CD4; Voltage Rating:500VDC; Capacitor Dielectric Material:Mica; Termination:Radial Leaded; Lead Pitch:2.5mm; Leaded Process Compatible:No RoHS Compliant: No |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X98027 | 制造商:XICOR 制造商全称:Xicor Inc. 功能描述:PRELIMINARY INFORMATION |

| X98027_06 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:275MHz Triple Video Digitizer with Digital PLL |

| X98027L128-3.3 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:275MHz Triple Video Digitizer with Digital PLL |

| X98027L128-3.3-Z | 功能描述:IC TRPL VID DIGITIZER 128MQFP RoHS:是 类别:集成电路 (IC) >> 线性 - 视频处理 系列:- 标准包装:250 系列:- 类型:电平移位器 应用:LCD 电视机/监控器 安装类型:表面贴装 封装/外壳:28-WFQFN 裸露焊盘 供应商设备封装:28-WQFN(4x4)裸露焊盘 包装:带卷 (TR) 其它名称:296-32523-2TPS65198RUYT-ND |

| X-98-499 | 制造商:Brady Corporation 功能描述:Labels External Width:1" |

发布紧急采购,3分钟左右您将得到回复。