- 您现在的位置:买卖IC网 > PDF目录19496 > XA2C64A-8VQG44Q (Xilinx Inc)IC CPLD 64MCELL 33 I/O 44-VQFP PDF资料下载

参数资料

| 型号: | XA2C64A-8VQG44Q |

| 厂商: | Xilinx Inc |

| 文件页数: | 13/16页 |

| 文件大小: | 0K |

| 描述: | IC CPLD 64MCELL 33 I/O 44-VQFP |

| 产品培训模块: | CoolRunner-II CPLD Starter Kit |

| 标准包装: | 160 |

| 系列: | CoolRunner II |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 6.7ns |

| 电压电源 - 内部: | 1.7 V ~ 1.9 V |

| 逻辑元件/逻辑块数目: | 4 |

| 宏单元数: | 64 |

| 门数: | 1500 |

| 输入/输出数: | 33 |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 44-TQFP |

| 供应商设备封装: | 44-VQFP(10x10) |

| 包装: | 托盘 |

XA2C64A CoolRunner-II Automotive CPLD

6

DS553 (v1.1) May 5, 2007

Product Specification

R

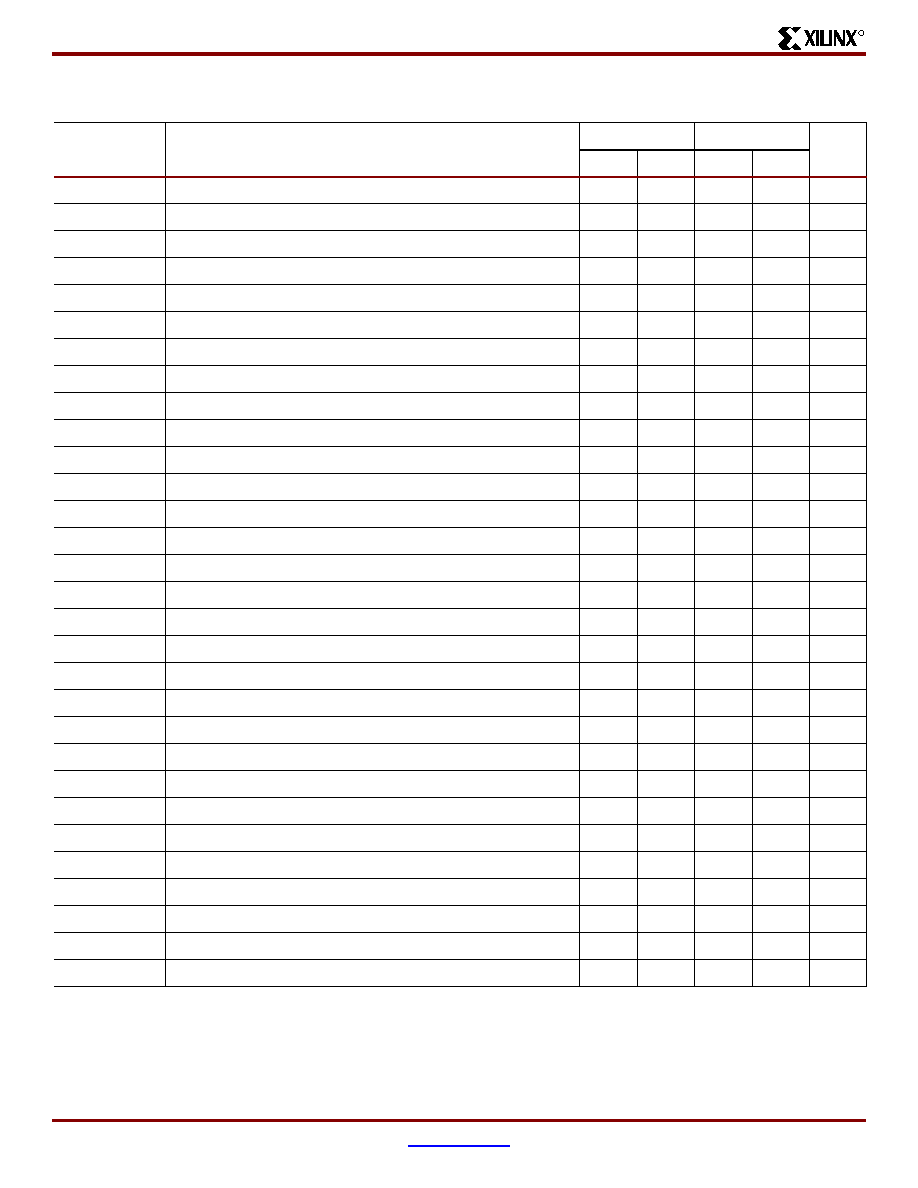

AC Electrical Characteristics Over Recommended Operating Conditions

Symbol

Parameter

-7

-8

Units

Min.

Max.

Min.

Max.

TPD1

Propagation delay single p-term

-

6.7

-

6.7

ns

TPD2

Propagation delay OR array

-

7.5

-

7.5

ns

TSUD

Direct input register clock setup time

3.3

-

3.3

-

ns

TSU1

Setup time (single p-term)

2.5

-

2.8

-

ns

TSU2

Setup time (OR array)

3.3

-

3.6

-

ns

THD

Direct input register hold time

0.0

-

0.0

-

ns

TH

P-term hold time

0.0

-

0.0

-

ns

TCO

Clock to output

-

6.0

-

6.0

ns

FTOGGLE(1)

Internal toggle rate(1)

-300

-

300

MHz

FSYSTEM1(2)

Maximum system frequency(2)

-159

-

152

MHz

FSYSTEM2(2)

Maximum system frequency(2)

-141

-

135

MHz

FEXT1(3)

Maximum external frequency(3)

-118

-

114

MHz

FEXT2(3)

Maximum external frequency(3)

-108

-

104

MHz

TPSUD

Direct input register p-term clock setup time

1.7

-

1.7

-

ns

TPSU1

P-term clock setup time (single p-term)

0.9

-

0.9

-

ns

TPSU2

P-term clock setup time (OR array)

1.7

-

1.7

-

ns

TPHD

Direct input register p-term clock hold time

1.4

-

1.4

-

ns

TPH

P-term clock hold

2.7

-

2.7

-

ns

TPCO

P-term clock to output

-

8.4

-

8.4

ns

TOE/TOD

Global OE to output enable/disable

-

10.0

-

10.0

ns

TPOE/TPOD

P-term OE to output enable/disable

-

11.0

-

11.0

ns

TMOE/TMOD

Macrocell driven OE to output enable/disable

-

11.0

-

11.0

ns

TPAO

P-term set/reset to output valid

-

9.7

-

9.7

ns

TAO

Global set/reset to output valid

-

8.3

-

8.3

ns

TSUEC

Register clock enable setup time

3.7

-

3.7

-

ns

THEC

Register clock enable hold time

0.0

-

0.0

-

ns

TCW

Global clock pulse width High or Low

2.2

-

2.2

-

ns

TPCW

P-term pulse width High or Low

7.5

-

7.5

-

ns

TAPRPW

Asynchronous preset/reset pulse width (High or Low)

7.5

-

7.5

-

ns

TCONFIG(4)

Configuration time

-

50.0

-

50

μs

Notes:

1.

FTOGGLE is the maximum frequency of a dual edge triggered T flip-flop with output enabled.

2.

FSYSTEM (1/TCYCLE) is the internal operating frequency for a device fully populated with 16-bit up/down, Resetable binary counter

(one counter per function block).

3.

FEXT (1/TSU1+TCO) is the maximum external frequency.

4.

Typical configuration current during

TCONFIG is 2.3 mA.

相关PDF资料 |

PDF描述 |

|---|---|

| ACM28DTMD-S189 | CONN EDGECARD 56POS R/A .156 SLD |

| RCB120DHLN | CONN EDGECARD 240PS DIP .050 SLD |

| KCM55WR71E476MH01K | CAP CER 47UF 25V 20% X7R 2220 |

| TAJB475K010H | CAP TANT 4.7UF 10V 10% 1210 |

| ACM28DTMN-S189 | CONN EDGECARD 56POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X-A2N | 制造商:Leach International Corporation 功能描述:EM RLY DPDT 5A 28VDC 500OHM SCKT - Bulk |

| XA2S100E-6FT256Q | 功能描述:IC FPGA SPARTAN-IIE 256FPBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA2S100E-6TQ144I | 功能描述:IC FPGA SPARTAN-IIE 144TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA2S100E-6TQ144Q | 功能描述:IC FPGA SPARTAN-IIE 144TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA2S150E-6FT256I | 功能描述:IC FPGA SPARTAN-IIE 256FPBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

发布紧急采购,3分钟左右您将得到回复。