参数资料

| 型号: | XA2S200E-6FT256Q |

| 厂商: | Xilinx Inc |

| 文件页数: | 1/6页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-IIE 256FPBGA |

| 产品变化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 标准包装: | 90 |

| 系列: | Spartan®-IIE XA |

| LAB/CLB数: | 1176 |

| 逻辑元件/单元数: | 5292 |

| RAM 位总计: | 57344 |

| 输入/输出数: | 182 |

| 门数: | 200000 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 125°C |

| 封装/外壳: | 256-LBGA |

| 供应商设备封装: | 256-FTBGA |

DS106-1 (v2.0) August 9, 2013

1

Product Specification

2002–2013 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

Introduction

The Xilinx Automotive (XA) Spartan-IIE 1.8V Field-Pro-

grammable Gate Array family is specifically designed to

meet the needs of high-volume, cost-sensitive automotive

electronic applications. The family gives users high perfor-

mance, abundant logic resources, and a rich feature set, all

at an exceptionally low price. The five-member family offers

densities ranging from 50,000 to 300,000 system gates, as

shown in Table 1. System performance is supported beyond

200 MHz.

Spartan-IIE devices deliver more gates, I/Os, and features

per dollar than other FPGAs by combining advanced pro-

cess technology with a streamlined architecture based on

the proven Virtex-E platform. Features include block RAM

(to 64K bits), distributed RAM (to 98,304 bits), 19 selectable

I/O standards, and four DLLs (Delay-Locked Loops). Fast,

predictable interconnect means that successive design iter-

ations continue to meet timing requirements.

XA devices are available in both the extended-temperature

Q-grade (-40°C to +125°C) and industrial I-grade (-40°C to

+100°C) and are qualified to the industry-recognized

AEC-Q100 standard.

The XA Spartan-IIE family is a superior alternative to

mask-programmed ASICs. The FPGA avoids the initial cost,

lengthy development cycles, and inherent risk of conven-

tional ASICs. Also, FPGA programmability permits design

upgrades in the field with no hardware replacement neces-

sary (impossible with ASICs).

Features

AEC-Q100 device qualification and full PPAP support

available in both extended temperature Q-grade and

I-grade

Guaranteed to meet full electrical specifications over

TJ = –40°C to +125°C

Second generation ASIC replacement technology

-

Densities as high as 6,912 logic cells with up to

300,000 system gates

-

Very low cost

System-level features

-

SelectRAM+ hierarchical memory:

16 bits/LUT distributed RAM

Configurable 4K-bit true dual-port block RAM

Fast interfaces to external RAM

-

Dedicated carry logic for high-speed arithmetic

-

Efficient multiplier support

-

Cascade chain for wide-input functions

-

Abundant registers/latches with enable, set, reset

-

Four dedicated DLLs for advanced clock control

Eliminate clock distribution delay

Multiply, divide, or phase shift

-

Four primary low-skew global clock distribution nets

-

IEEE 1149.1 compatible boundary scan logic

Versatile I/O and packaging

-

Low-cost packages available in all densities

-

19 high-performance interface standards

LVTTL, LVCMOS, HSTL, SSTL, AGP, CTT, GTL

LVDS and LVPECL differential I/O

-

Up to 120 differential I/O pairs that can be input,

output, or bidirectional

Fully supported by powerful Xilinx ISE development

system

-

Fully automatic mapping, placement, and routing

-

Integrated with design entry and verification tools

-

Extensive IP library including DSP functions

0

Spartan-IIE 1.8V FPGA

Automotive XA Product Family:

Introduction and Ordering

DS106-1 (v2.0) August 9, 2013

00

Product Specification

R

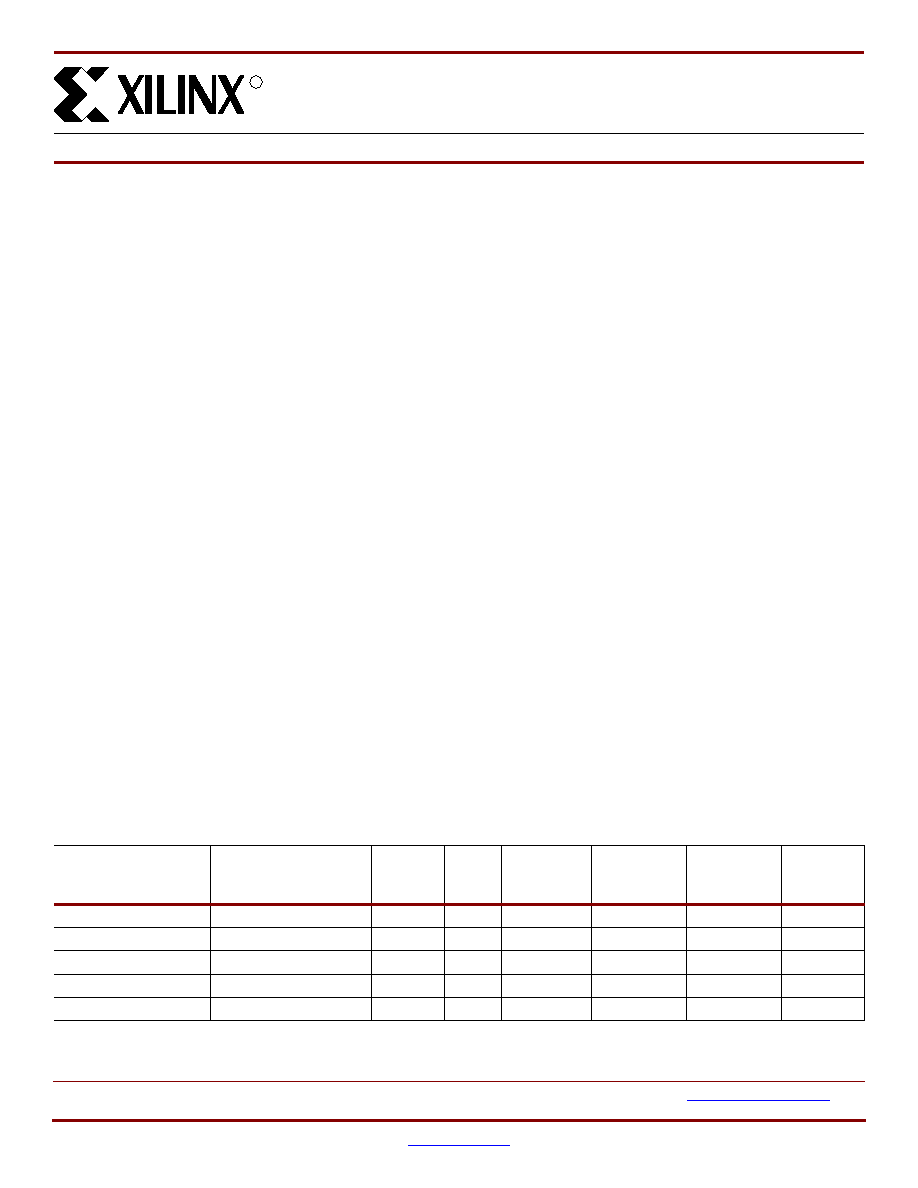

Table 1: XA Spartan-IIE FPGA Family Members

Device

Logic

Cells

Typical

System Gate Range

(Logic and RAM)

CLB

Array

(R x C)

Total

CLBs

Maximum

Available

User I/O(1)

Maximum

Differential

I/O Pairs

Distributed

RAM Bits

Block

RAM Bits

XA2S50E

1,728

23,000 - 50,000

16 x 24

384

102

83

24,576

32K

XA2S100E

2,700

37,000 - 100,000

20 x 30

600

102

86

38,400

40K

XA2S150E

3,888

52,000 - 150,000

24 x 36

864

182

114

55,296

48K

XA2S200E

5,292

71,000 - 200,000

28 x 42

1,176

182

120

75,264

56K

XA2S300E

6,912

93,000 - 300,000

32 x 48

1,536

182

120

98,304

64K

Notes:

1.

User I/O counts include the four global clock/user input pins. See details in Table 3, page 5

相关PDF资料 |

PDF描述 |

|---|---|

| 93AA86AT-I/MS | IC EEPROM 16KBIT 2048X8 8-MSOP |

| XC3S700A-5FG400C | IC SPARTAN-3A FPGA 700K 400FBGA |

| XC2S200-5FG456C | IC FPGA 2.5V 1176 CLB'S 456-FBGA |

| 93AA86CT-I/MNY | IC EEPROM SER 16K 1.8V 8TDFN |

| 93LC86A-E/SN | IC EEPROM 16KBIT 3MHZ 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XA2S300E-6FT256I | 功能描述:IC FPGA SPARTAN-IIE 256FPBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA2S300E-6FT256Q | 功能描述:IC FPGA SPARTAN-IIE 256FPBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA2S50E-6TQ144I | 功能描述:IC FPGA SPARTAN-IIE 144TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA2S50E-6TQ144Q | 功能描述:IC FPGA SPARTAN-IIE 144TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-IIE XA 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XA-30-3213-01 | 制造商:Misc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。