参数资料

| 型号: | XA95144XL-15CSG144I |

| 厂商: | Xilinx Inc |

| 文件页数: | 3/5页 |

| 文件大小: | 0K |

| 描述: | IC CPLD 144MC 117 I/O 144CSBGA |

| 标准包装: | 198 |

| 系列: | XA9500XL XA |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 15.5ns |

| 电压电源 - 内部: | 3 V ~ 3.6 V |

| 逻辑元件/逻辑块数目: | 8 |

| 宏单元数: | 144 |

| 门数: | 3200 |

| 输入/输出数: | 117 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-TFBGA,CSPBGA |

| 供应商设备封装: | 144-LCSBGA(12x12) |

| 包装: | 托盘 |

XA9500XL Automotive CPLD Product Family

DS108-1 (v1.7) April 3, 2007

3

Product Specification

R

Component Availability

Ordering Information

XA9500XL Automotive Requirements and Recommendations

Requirements

The following requirements are for all automotive applica-

tions:

1. All automotive customers are required to keep the

Macrocell Power selection set to low, and the Logic

Optimization set to density when designing with ISE

software. These are the default settings when

XA9500XL devices are selected for design. These

settings are found on the Process Properties page for

Implement Design. See the ISE Online Help for details

on these properties.

2. Use a monotonic, fast ramp power supply to power up

XA9500XL . A VCC ramp time of less than 1 ms is

required.

3. Do not float I/O pins during device operation. Floating

I/O pins can increase ICC as input buffers will draw

1-2 mA per floating input. In addition, when I/O pins are

floated, noise can propagate to the center of the CPLD.

I/O pins should be appropriately terminated with

keeper/bus-hold. Unused I/Os can also be configured

as CGND (programmable GND).

4. Do not drive I/O pins without VCC/VCCIO powered.

5. Sink current when driving LEDs. Because all Xilinx

CPLDs have N-channel pull-down transistors on

outputs, it is required that an LED anode is sourced

through a resistor externally to VCC. Consequently, this

will give the brightest solution.

6. Avoid external pull-down resistors. Always use external

pull-up resistors if external termination is required. This

is because the XA9500XL Automotive CPLD, which

includes some I/O driving circuits beyond the input and

output buffers, may have contention with external

pull-down resistors, and, consequently, the I/O will not

switch as expected.

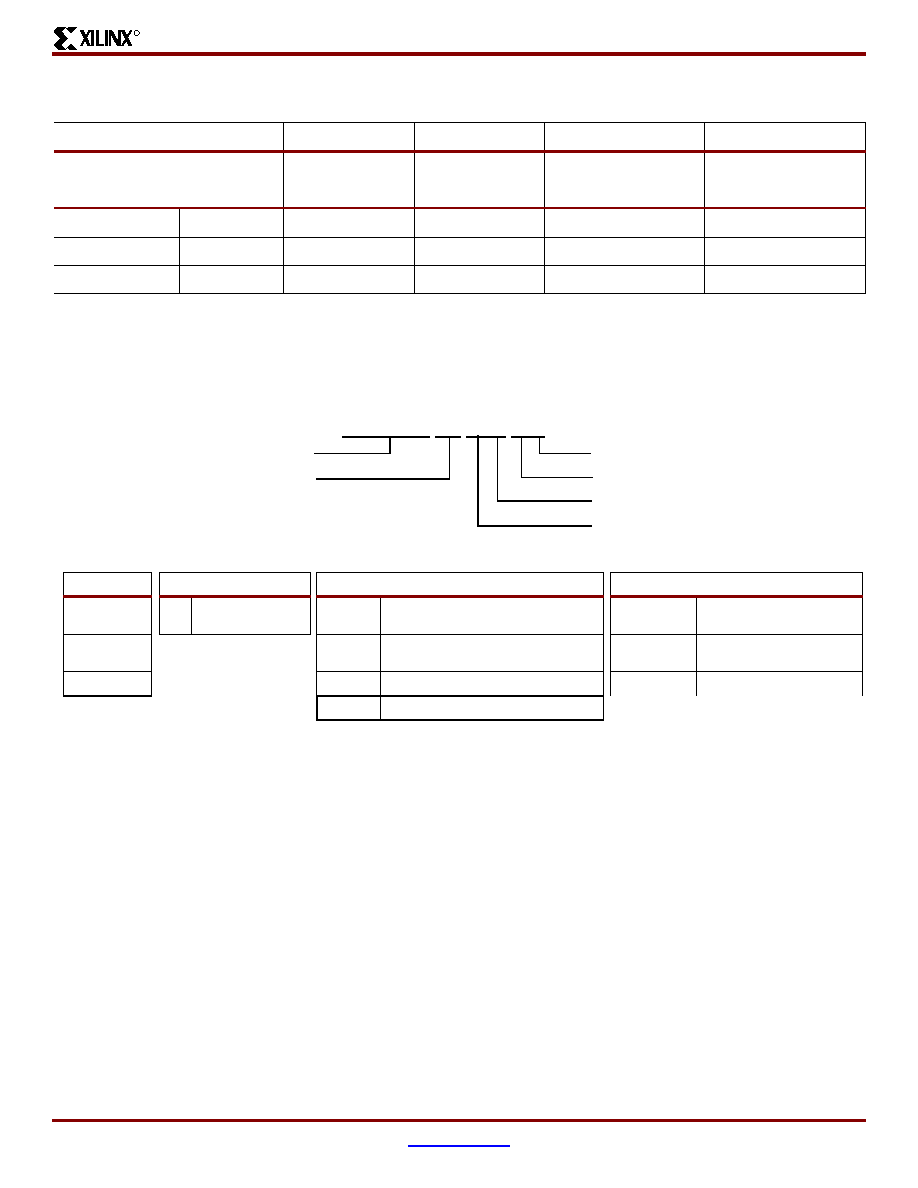

Pins

44

64

100

144

Type

Quad Flat Pack

Thin Quad Flat Pack

Chip Scale Package

Code

VQG44

VQG64

TQG100

CSG144

XA9536XL

-15

I,Q

--

XA9572XL

-15

I,Q

--

XA95144XL

-15

--

I

Notes:

1.

Q = Automotive Extended Temperature (TA = –40°C to +105°C).

2.

I = Automotive Industrial Temperature (TA = –40°C to +85°C).

3.

All packages Pb-free.

XA9572XL -15 VQG 44Q

Example:

Temperature Range

Number of Pins

Pb-free

Package Type

Device Type

Speed Grade

Device Ordering Options

Device

Speed

Package

Temperature

XA9536XL

-15 15.5 ns pin-to-pin

delay

VQG44 44-pin Quad Flat Pack (VQFP)

I-Grade

TA = –40°C to +85°C

XA9572XL

VQG64 64-pin Quad Flat Pack (VQFP)

Q-Grade

TA = –40°C to +105°C with

TJ Maximum = 125°C

XA95144XL

TQG100 100-pin Thin Quad Flat Pack (TQFP)

CSG144 144-pin Chip Scale Package (CSP)

相关PDF资料 |

PDF描述 |

|---|---|

| XAM1808AZCE4 | IC ARM PROCESSOR 361NFBGA |

| XC1765ESOG8C | IC PROM SERIAL 65K 8-SOIC |

| XC17S200AVQ44I | IC PROM SER 200000 I-TEMP 44VQFP |

| XC17S30XLVOG8I | IC PROM SERIAL 3.3V 300K 8-SOIC |

| XC17V08VQ44I | IC PROM SER I-TEMP 3.3V 44-VQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XA9536XL-10VQ44I | 制造商:Xilinx 功能描述: |

| XA9536XL-10VQ44Q | 制造商:Xilinx 功能描述: |

| XA9536XL-15VQG44I | 功能描述:IC CPLD 3.3V 36MCELL 44-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:XA9500XL XA 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| XA9536XL-15VQG44Q | 功能描述:IC CPLD 3.3V 36MCELL 44-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:XA9500XL XA 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

| XA9572XL-10TQ100I | 制造商:Xilinx 功能描述: |

发布紧急采购,3分钟左右您将得到回复。