- 您现在的位置:买卖IC网 > PDF目录19877 > XC17V08PC44C (Xilinx Inc)IC PROM SER C-TEMP 3.3V 44-PLCC PDF资料下载

参数资料

| 型号: | XC17V08PC44C |

| 厂商: | Xilinx Inc |

| 文件页数: | 9/15页 |

| 文件大小: | 0K |

| 描述: | IC PROM SER C-TEMP 3.3V 44-PLCC |

| 产品变化通告: | Product Discontinuation Notice 14/May/2007 |

| 标准包装: | 26 |

| 可编程类型: | OTP |

| 存储容量: | 8Mb |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 70°C |

| 封装/外壳: | 44-LCC(J 形引线) |

| 供应商设备封装: | 44-PLCC(16.59x16.59) |

| 包装: | 管件 |

XC17V00 Series Configuration PROMs

DS073 (v2.0) April 7, 2014

Product Specification

3

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

Pin Description

DATA[0:7]

The array data value corresponding to the internal address

counter location is output on enabled DATA[0-7] output

pin(s) when CE is active, OE is active, and the internal

address counter has not incremented beyond its Terminal

Count (TC) value. Otherwise, all data pins are in a high

impedance state when CE is inactive, OE is inactive, or the

internal address counter has incremented beyond its

Terminal Count (TC) value.

The XC17V01, XC17V02, and XC17V04 have only the

single DATA output pin for connection to the FPGA serial

configuration data input pin.

The XC17V08 and XC17V16 have the D[0-7] output pins.

During device programming, the XC17V08 and XC17V16

must be programmed for use in either serial output mode or

parallel output mode. For XC17V08 and XC17V16 devices

programmed to serial output mode, only the D0 pin is

enabled for data output to the Virtex series FPGA serial

configuration data input pin. In serial mode, the D[1-7]

output pins remain in high impedance state and may be

unconnected. For XC17V08 and XC17V16 devices

programmed to parallel output mode, all D[0-7] output pins

are enabled for byte-wide data output to the FPGA

SelectMAP configuration data input pins.

The DATA/D0 pin is a bidirectional I/O during device

programming.

CLK

Each rising edge on the CLK input increments the internal

address counter, when CE is active, OE is active, the

internal address counter has not incremented past its

Terminal Count (TC) value, and BUSY is Low.

Note: The BUSY condition applies to only the XC17V08 and

XC17V16.

RESET/OE

The polarity of this input pin is programmable as either

RESET/OE or OE/RESET. The polarity is set at the time of

device programming. The device default is active-High

RESET, but compatibility with Xilinx FPGAs requires the

polarity to be programmed with an active-Low RESET.

When RESET is active, the address counter is held at “0”,

and puts the DATA output in a high-impedance state.

CE

When High, this pin holds the internal address counter in

reset, puts the DATA output in a high-impedance state, and

forces the device into low-ICC standby mode.

CEO

Chip Enable Output is connected to the CE input of the next

PROM in the daisy chain. This output is Low when the CE

and OE inputs are both active AND the internal address

counter has been incremented beyond its Terminal Count

(TC) value. CEO returns to High when OE goes inactive or

CE goes High.

BUSY (XC17V16 and XC17V08 Only)

Asserting the BUSY input High prevents rising edges on

CLK from incrementing the internal address counter and

maintains current data on the data pins.

Note: If the BUSY pin is floating, then the programmable option

to internally tie BUSY to an internal pull-down resistor must be set

during device programming.

VPP

Programming voltage. No overshoot above the specified

maximum voltage is permitted on this pin. For normal read

operation, this pin must be connected to VCC. Failure to do

so may lead to unpredictable, temperature-dependent

operation and severe problems in circuit debugging.

Caution! Do not leave VPP floating!

VCC and GND

Positive supply and ground pins.

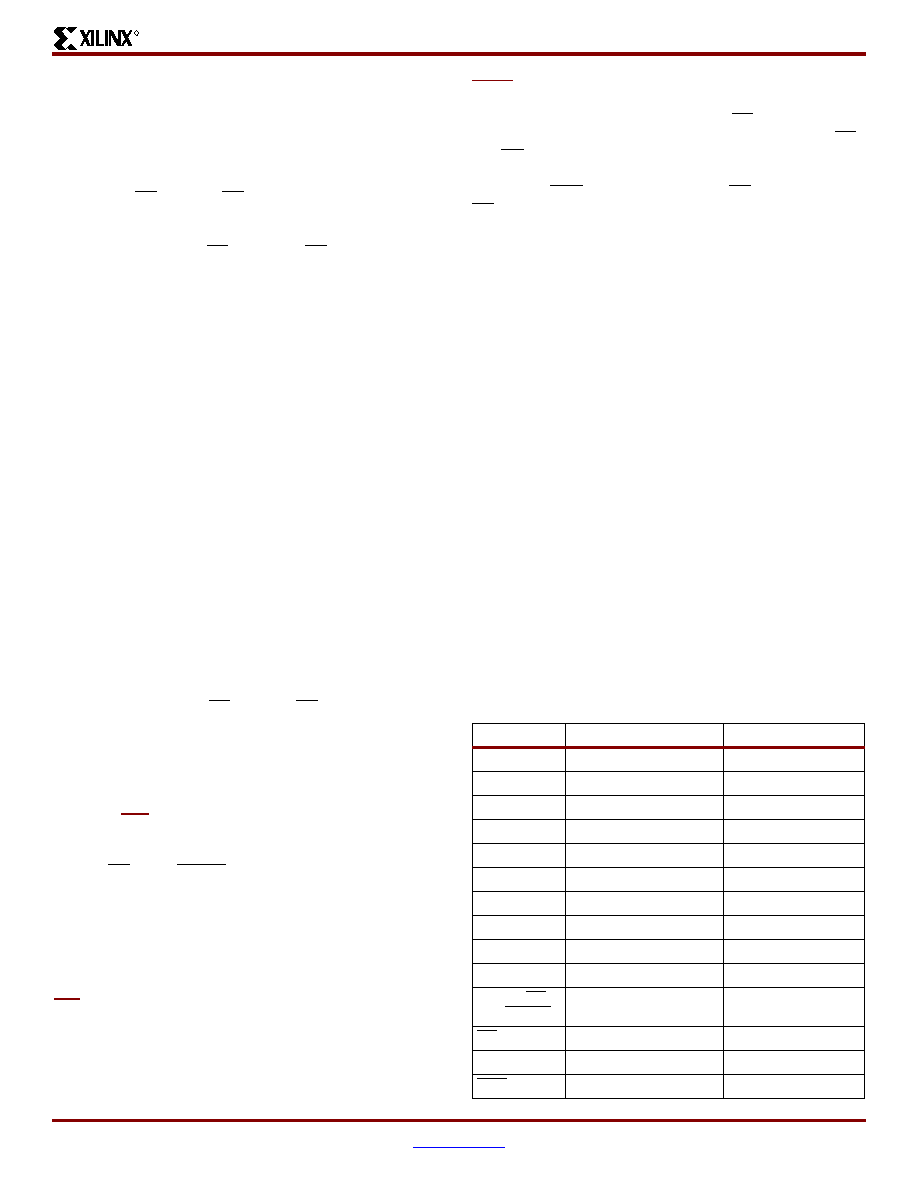

PROM Pinouts for XC17V16 and XC17V08

Pins not listed in Table 1 are “no connect.”

Table 1: Pinouts for XC17V16 and XC17V08(1)

Pin Name

44-pin VQFP (VQ44)

44-pin PLCC (PC44)

BUSY

24

30

D0

40

2

D1

29

35

D2

42

4

D3

27

33

D4

9

15

D5

25

31

D6

14

20

D7

19

25

CLK

43

5

RESET/OE

(OE/RESET)

13

19

CE

15

21

GND

6, 18, 28, 37, 41

3, 12, 24, 34, 43

CEO

21

27

相关PDF资料 |

PDF描述 |

|---|---|

| XC17V02PC20C | IC PROM SER 2MBIT 3.3V 20-PLCC |

| TPSD475K050R0300 | CAP TANT 4.7UF 50V 10% 2917 |

| R15P215S/P | CONV DC/DC 2W 15VIN 15VOUT |

| ESM36DTMD-S273 | CONN EDGECARD 72POS R/A .156 SLD |

| GRM21BF51A155ZA01L | CAP CER 1.5UF 10V Y5V 0805 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC17V08PC44I | 功能描述:IC PROM SER I-TEMP 3.3V 44-PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 - 用于 FPGA 的配置 Proms 系列:- 产品变化通告:Product Discontinuation 28/Jul/2010 标准包装:98 系列:- 可编程类型:OTP 存储容量:300kb 电源电压:3 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-TSOP 包装:管件 |

| XC17V08SERIES | 制造商:未知厂家 制造商全称:未知厂家 功能描述:XC17V00 Series Configuration PROM |

| XC17V08SO20C | 制造商:XILINX 制造商全称:XILINX 功能描述:XC17V00 Series Configuration PROM |

| XC17V08SO20I | 制造商:XILINX 制造商全称:XILINX 功能描述:XC17V00 Series Configuration PROM |

| XC17V08V08C | 制造商:XILINX 制造商全称:XILINX 功能描述:XC17V00 Series Configuration PROM |

发布紧急采购,3分钟左右您将得到回复。