- 您现在的位置:买卖IC网 > PDF目录19828 > XC2C256-7TQG144I (Xilinx Inc)IC CR-II CPLD 256MCELL 144-TQFP PDF资料下载

参数资料

| 型号: | XC2C256-7TQG144I |

| 厂商: | Xilinx Inc |

| 文件页数: | 16/16页 |

| 文件大小: | 0K |

| 描述: | IC CR-II CPLD 256MCELL 144-TQFP |

| 标准包装: | 60 |

| 系列: | CoolRunner II |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 6.7ns |

| 电压电源 - 内部: | 1.7 V ~ 1.9 V |

| 逻辑元件/逻辑块数目: | 16 |

| 宏单元数: | 256 |

| 门数: | 6000 |

| 输入/输出数: | 118 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-TQFP(20x20) |

| 包装: | 托盘 |

| 配用: | 122-1573-ND - KIT STARTER COOLRUNNER-II LP/LC 122-1512-ND - KIT DESIGN CPLD W/BATT HOLDER |

| 其它名称: | 122-1703 XC2C256-7TQG144I-ND |

CoolRunner-II CPLD Family

DS090 (v3.1) September 11, 2008

Product Specification

R

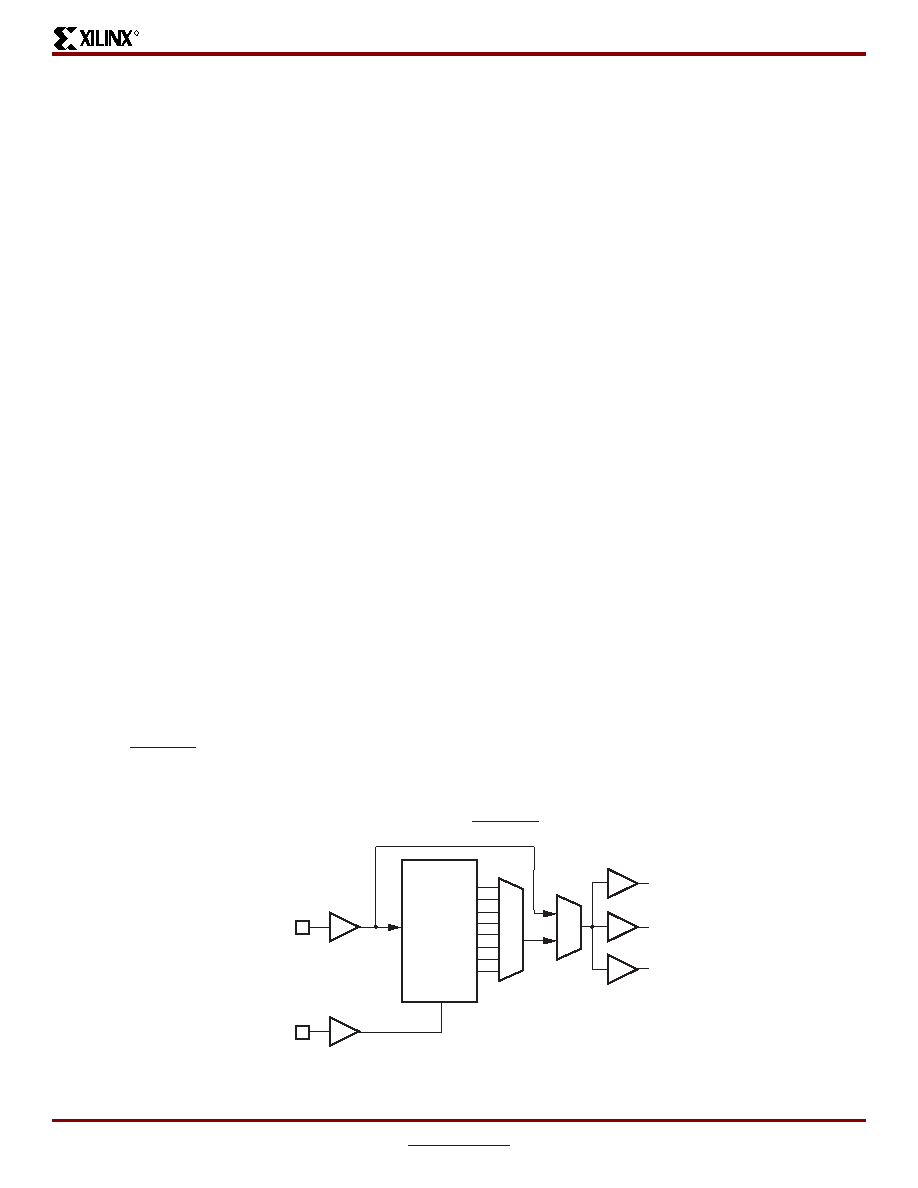

Additional Clock Options: Division,

DualEDGE, and CoolCLOCK

Clock Divider

A

clock

divider

circuit

has

been

included

in

the

CoolRunner-II CPLD architecture to divide one externally

supplied global clock by standard values. The allowable val-

ues for the division are 2, 4, 6, 8, 10, 12, 14, and 16 (see

Figure 8). This capability is supplied on the GCK2 pin. The

resulting clock produced has a 50% duty cycle for all possi-

ble divisions. The output of the clock divider is on global

routing. If the clock divider is used, the undivided clock is

available internally. If the undivided clock is required inter-

nally it is input through a separate clock pin.

The clock divider circuit encompasses a synchronous reset

(CDRST) to guarantee no spurious clocks can carry

through on to the global clock nets. When the CDRST signal

is asserted, the clock divider output is disabled after the cur-

rent cycle. When the CDRST signal is deasserted the clock

divider output becomes active upon the first edge of GCK2.

The CDRST pin functions as a reset pin regardless of which

CLK_DIV primitive is used. If a clock divider is used in the

design, the CDRST pin is reserved and if it is driven High

the clock divider is reset. If a reset port of a clock divider is

not used, it is tied Low on the board. The clock divider circuit

includes an active High synchronous reset, referred to as

CDRST.

The CoolRunner-II CPLD clock divider includes a built-in

delay circuit. With the delay feature enabled, the output of

the clock divider is delayed for one full count cycle. When

used, the clock divider does not output a rising clock edge

until after the divider reaches the delay value. The delay fea-

ture is either enabled or disabled upon configuration.

Xilinx Synthesis Technology (XST) allows a clock divider

component to be instantiated directly in the HDL source

code. See XAPP378 for instantiation examples in VHDL,

Verilog, and ABEL.

DualEDGE

Each macrocell has the ability to double its input clock

switching frequency. Figure 9 shows the macrocell flip-flop

with the DualEDGE option (doubled clock) at each macro-

cell. The source to double can be a control term clock, a

product term clock or one of the available global clocks. The

ability to switch on both clock edges, also known as dual

edge triggered (DET), is vital for a number of synchronous

memory interface applications as well as certain double

data rate I/O applications.

CoolRunner-II CPLD DET registers can be used for logic

functions that include shift registers, counters, comparators,

and state machines. Designers must evaluate the desired

performance of the CPLD logic to determine use of DET

registers.

The DET register can be inferred in any ABEL, HDL, or

schematic design. A designer can infer a single-edge trig-

gered (SET) register in any HDL design. The DET register is

available with all macrocells in all devices of the

CoolRunner-II family.

CoolCLOCK

In addition to the DualEDGE flip-flop, power savings can

occur by combining the clock division circuitry with the

DualEDGE circuitry. This capability is called CoolCLOCK

and is designed to reduce clocking power within the CPLD.

Because the clock net can be an appreciable power drain,

the clock power can be reduced by driving the net at half fre-

quency, then doubling the clock rate using DualEDGE trig-

gering at the macrocells. Figure 10 shows how CoolCLOCK

is created by internal clock cascading with the divider and

DualEDGE flip-flop working together.

GCK2 is the only clock network that can be divided, the

CoolCLOCK feature is only available on GCK2. The Cool-

CLOCK feature can be implemented by assigning an

attribute to an input clock. The CoolCLOCK attribute

replaces the need to instantiate the clock divider and infer

DET registers. The CoolCLOCK feature is available on

CoolRunner-II 128 macrocell devices and larger. See

XAPP378 for more detail.

Figure 8: Clock Division Circuitry for GCK2

DS090_08_121201

Clock

In

÷2

÷4

÷6

÷8

÷10

÷12

÷14

÷16

GCK2

CDRST

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B1F-CY-F3 | CONVERTER MOD DC/DC 72V 50W |

| ISL6119HIBZA | IC CTRLR USB DUAL PORT OC 8SOIC |

| CWR29KK106KBGZ | CAP TANT 10UF 25V 10% 2711 |

| VI-B1F-CY-F2 | CONVERTER MOD DC/DC 72V 50W |

| VE-24V-CY-B1 | CONVERTER MOD DC/DC 5.8V 50W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2C256-7VQ100C | 制造商:Xilinx 功能描述:IC SYSTEM GATE 制造商:Xilinx 功能描述:CPLD COOLRUNNER-II 6K GATES 256 MCRCLLS 300MHZ 0.18UM 1.8V 1 - Trays 制造商:Xilinx 功能描述:IC CPLD 256MC 6.7NS 100VQFP 制造商:Xilinx 功能描述:IC CR-II CPLD 256MCELL 100-VQFP |

| XC2C256-7VQ100CES | 制造商:Xilinx 功能描述: |

| XC2C256-7VQ100I | 制造商:Xilinx 功能描述:IC SYSTEM GATE 制造商:Xilinx 功能描述:CPLD COOLRUNNER-II 6K GATES 256 MCRCLLS 300MHZ 0.18UM 1.8V 1 - Trays 制造商:Xilinx 功能描述:IC CR-II CPLD 256MCELL 100-VQFP 制造商:Xilinx 功能描述:IC CPLD 256MC 6.7NS 100VQFP 制造商:Xilinx 功能描述:COMPLEX-EEPLD, 256-CELL, 7.5NS PROP DELAY, 100 Pin, Plastic, TQFP |

| XC2C256-7VQG100C | 功能描述:IC CR-II CPLD 256MCELL 100-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:90 系列:ispMACH® 4A 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.5ns 电压电源 - 内部:4.75 V ~ 5.25 V 逻辑元件/逻辑块数目:- 宏单元数:64 门数:- 输入/输出数:48 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:100-LQFP 供应商设备封装:100-TQFP(14x14) 包装:托盘 |

| XC2C256-7VQG100I | 功能描述:IC CR-II CPLD 256MCELL 100-VQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner II 标准包装:24 系列:CoolRunner II 可编程类型:系统内可编程 最大延迟时间 tpd(1):7.1ns 电压电源 - 内部:1.7 V ~ 1.9 V 逻辑元件/逻辑块数目:24 宏单元数:384 门数:9000 输入/输出数:173 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。