参数资料

| 型号: | XC2S200E-6FGG456C |

| 厂商: | Xilinx Inc |

| 文件页数: | 20/108页 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-IIE FPGA 200K 456FBGA |

| 标准包装: | 60 |

| 系列: | Spartan®-IIE |

| LAB/CLB数: | 1176 |

| 逻辑元件/单元数: | 5292 |

| RAM 位总计: | 57344 |

| 输入/输出数: | 289 |

| 门数: | 200000 |

| 电源电压: | 1.71 V ~ 1.89 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 456-BBGA |

| 供应商设备封装: | 456-FBGA |

| 其它名称: | 122-1323 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

DS077-2 (v3.0) August 9, 2013

19

Product Specification

Spartan-IIE FPGA Family: Functional Description

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

The public boundary-scan instructions are available prior to

configuration, except for USER1 and USER2. After configu-

ration, the public instructions remain available together with

any USERCODE instructions installed during the configura-

tion. While the SAMPLE/PRELOAD and BYPASS instruc-

tions are available during configuration, it is recommended

that boundary-scan operations not be performed during this

transitional period.

In addition to the test instructions outlined above, the

boundary-scan circuitry can be used to configure the

FPGA, and also to read back the configuration data.

To facilitate internal scan chains, the User Register provides

three outputs (Reset, Update, and Shift) that represent the

corresponding states in the boundary-scan internal state

machine.

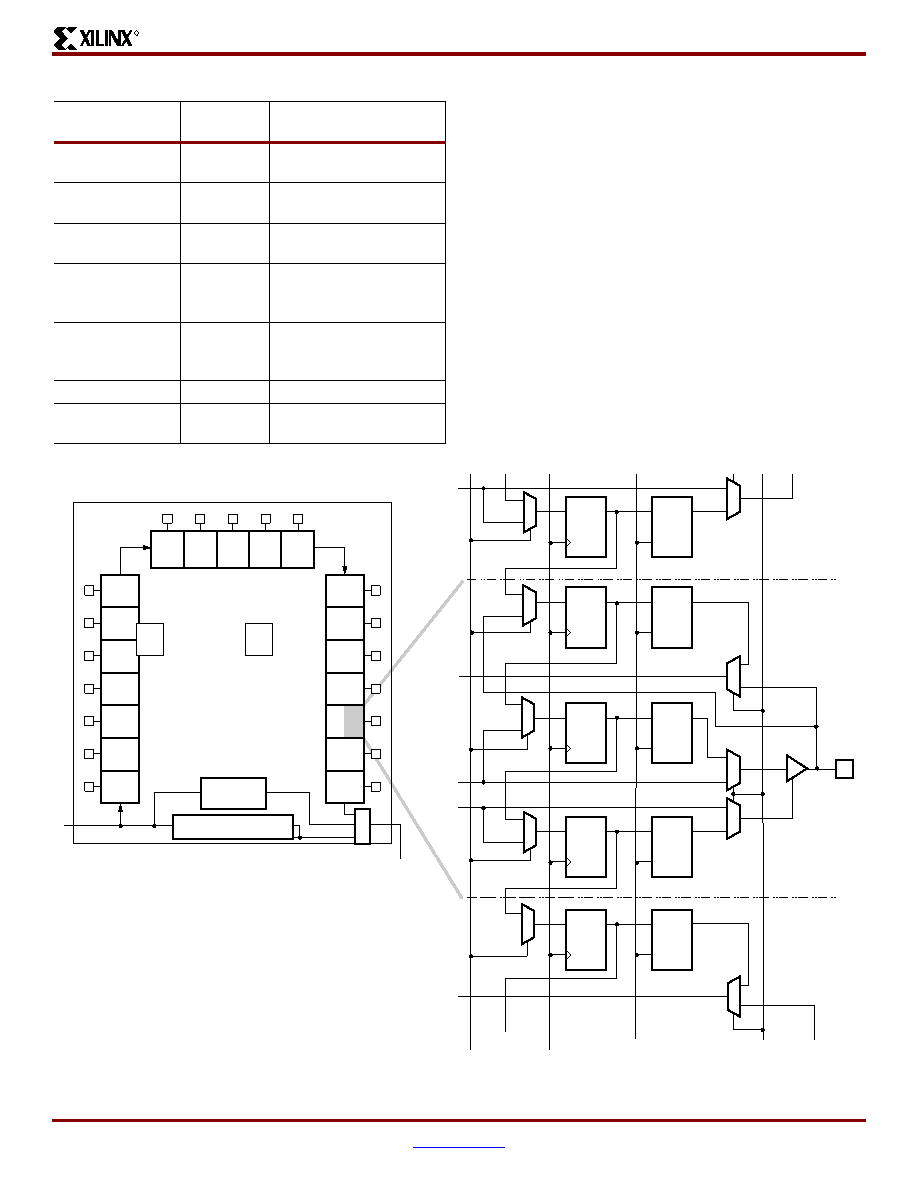

Figure 14 is a diagram of the Spartan-IIE family boundary

scan logic. It includes three bits of Data Register per IOB,

the IEEE 1149.1 Test Access Port controller, and the

Instruction Register with decodes.

INTEST

00111

Enables boundary-scan

INTEST operation

USERCODE

01000

Enables shifting out

USER code

IDCODE

01001

Enables shifting out of

ID Code

HIGHZ

01010

Disables output pins

while enabling the

Bypass Register

JSTART

01100

Clock the start-up

sequence when

StartupClk is TCK

BYPASS

11111

Enables BYPASS

RESERVED

All other

codes

Xilinx reserved

instructions

Table 8: Boundary-Scan Instructions (Continued)

Boundary-Scan

Command

Binary

Code[4:0]

Description

Figure 14: Spartan-IIE Family Boundary Scan Logic

D

Q

D

Q

IOB

M

U

X

Bypass

Register

IOB

TDO

TDI

IOB

1

0

1

0

1

0

1

0

1

0

sd

LE

DQ

D

Q

D

Q

1

0

1

0

1

0

1

0

DQ

LE

sd

LE

DQ

sd

LE

DQ

IOB

D

Q

1

0

DQ

LE

sd

IOB.T

DATA IN

IOB.I

IOB.Q

IOB.T

IOB.I

SHIFT/

CAPTURE

CLOCK DATA

REGISTER

DATAOUT

UPDATE

EXTEST

DS001_09_032300

Instruction Register

相关PDF资料 |

PDF描述 |

|---|---|

| XC2S200E-6FG456C | IC FPGA 1.8V 1176 CLB'S 456-FPGA |

| 93C86CT-E/SN | IC EEPROM 16KBIT 3MHZ 8SOIC |

| XA6SLX16-2FTG256Q | IC FPGA SPARTAN 6 256FTGBGA |

| GMC20DTEN | CONN EDGECARD 40POS .100 EYELET |

| 93C86C-E/SN | IC EEPROM 16KBIT 3MHZ 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2S200E-6FGG456I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S200E-6FGG676C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S200E-6FGG676I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S200E6FT256C | 制造商:Xilinx 功能描述: |

| XC2S200E-6FT256C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-IIE 1.8V FPGA Family |

发布紧急采购,3分钟左右您将得到回复。