参数资料

| 型号: | XC4006E-4PG156I |

| 厂商: | Xilinx Inc |

| 文件页数: | 4/68页 |

| 文件大小: | 0K |

| 描述: | IC FPGA I-TEMP 5V 4SPD 156-CPGA |

| 产品变化通告: | XC4000(E,L) Discontinuation 01/April/2002 |

| 标准包装: | 14 |

| 系列: | XC4000E/X |

| LAB/CLB数: | 256 |

| 逻辑元件/单元数: | 608 |

| RAM 位总计: | 8192 |

| 输入/输出数: | 125 |

| 门数: | 6000 |

| 电源电压: | 4.5 V ~ 5.5 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 156-BCBGA |

| 供应商设备封装: | 156-CPGA(42.17x42.17) |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

R

XC4000E and XC4000X Series Field Programmable Gate Arrays

6-16

May 14, 1999 (Version 1.6)

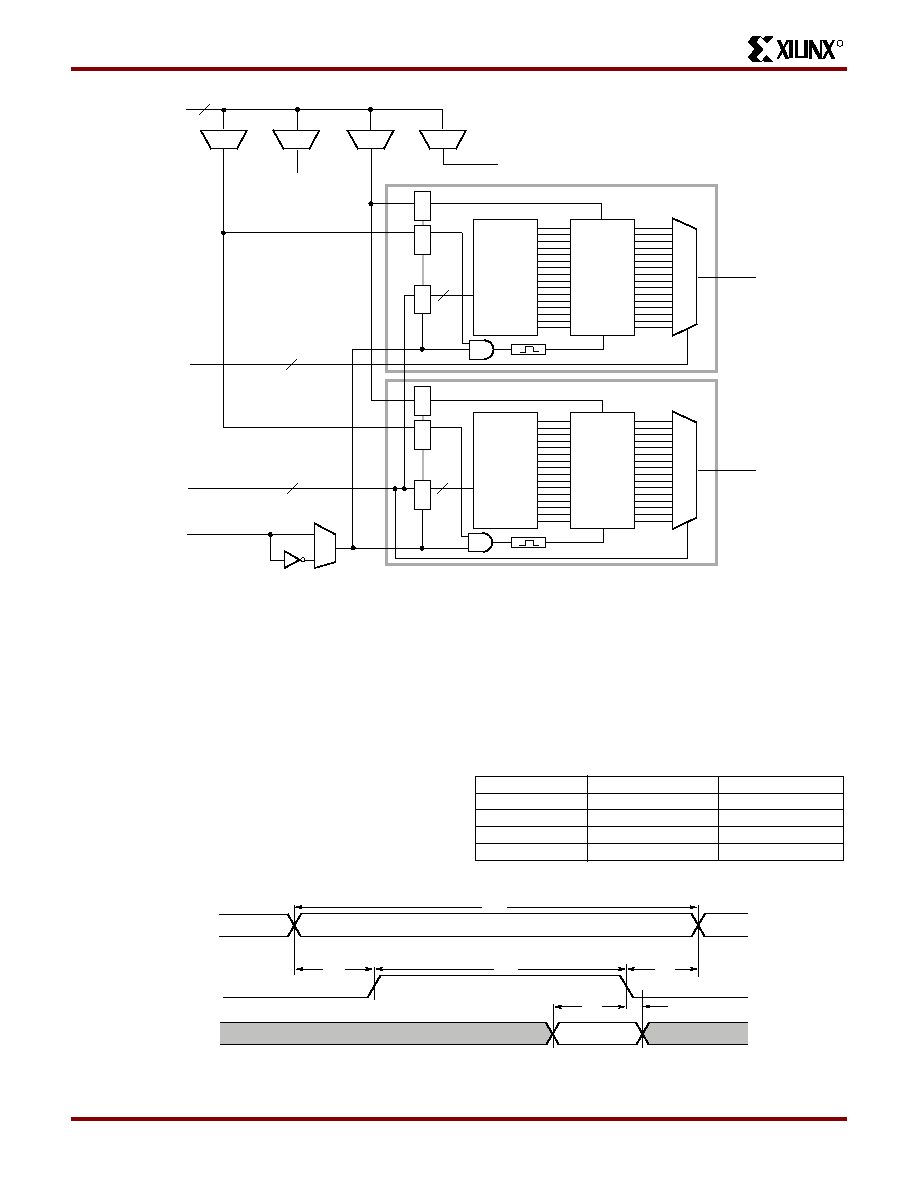

Figure 8 shows the write timing for level-sensitive, sin-

gle-port RAM.

The relationships between CLB pins and RAM inputs and

outputs for single-port level-sensitive mode are shown in

gured as 16x2 and 32x1 level-sensitive, single-port RAM.

Initializing RAM at Conguration

Both RAM and ROM implementations of the XC4000

Series devices are initialized during conguration. The ini-

tial contents are dened via an INIT attribute or property

attached to the RAM or ROM symbol, as described in the

schematic library guide. If not dened, all RAM contents

are initialized to all zeros, by default.

RAM initialization occurs only during conguration. The

RAM content is not affected by Global Set/Reset.

Table 7: Single-Port Level-Sensitive RAM Signals

G'

G1 G4

F1 F4

WRITE

DECODER

1 of 16

DIN

16-LATCH

ARRAY

X6748

4

MUX

F'

WRITE

DECODER

1 of 16

DIN

16-LATCH

ARRAY

READ

ADDRESS

READ

ADDRESS

WRITE PULSE

LATCH

ENABLE

LATCH

ENABLE

K

(CLOCK)

WRITE PULSE

MUX

4

C1 C4

4

WE

D1

D0

EC

Figure 7: 16x1 Edge-Triggered Dual-Port RAM

RAM Signal

CLB Pin

Function

D

D0 or D1

Data In

A[3:0]

F1-F4 or G1-G4

Address

WE

Write Enable

O

F’ or G’

Data Out

WC

T

ADDRESS

WRITE ENABLE

DATA IN

AS

T

WP

T

DS

T

DH

T

REQUIRED

AH

T

X6462

Figure 8: Level-Sensitive RAM Write Timing

Product Obsolete or Under Obsolescence

相关PDF资料 |

PDF描述 |

|---|---|

| XC4006E-4PG156C | IC FPGA C-TEMP 5V 4SPD 156-CPGA |

| XC4006E-4PC84I | IC FPGA I-TEMP 5V 4SPD 84-PLCC |

| 487378-9 | CONN RECEPT 10POS .100 SLIMLINE |

| 487378-1 | CONN RECEPT 2POS .100 SLIMLINE |

| ASM43DRAN | CONN EDGECARD 86POS .156 R/A |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC4006E-4PG156M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Field Programmable Gate Array (FPGA) |

| XC4006E-4PQ160C | 功能描述:IC FPGA 256 CLB'S 160-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:XC4000E/X 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC4006E-4PQ160I | 功能描述:IC FPGA I-TEMP 5V 4SPD 160-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:XC4000E/X 标准包装:1 系列:Kintex-7 LAB/CLB数:25475 逻辑元件/单元数:326080 RAM 位总计:16404480 输入/输出数:350 门数:- 电源电压:0.97 V ~ 1.03 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:900-BBGA,FCBGA 供应商设备封装:900-FCBGA(31x31) 其它名称:122-1789 |

| XC4006E-4PQ160I0377 | 制造商:Xilinx 功能描述: |

| XC4006E4PQ208C | 制造商:XILINX 功能描述:* |

发布紧急采购,3分钟左右您将得到回复。