- 您现在的位置:买卖IC网 > PDF目录300144 > XC4013E-3BG240M (Xilinx, Inc.) XC4000E and XC4000X Series Field Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | XC4013E-3BG240M |

| 厂商: | Xilinx, Inc. |

| 英文描述: | XC4000E and XC4000X Series Field Programmable Gate Arrays |

| 中文描述: | XC4000E和XC4000X系列现场可编程门阵列 |

| 文件页数: | 4/4页 |

| 文件大小: | 21K |

| 代理商: | XC4013E-3BG240M |

4

XC4000E Logic Cell Array Family

ADVANCE

INFORMATION

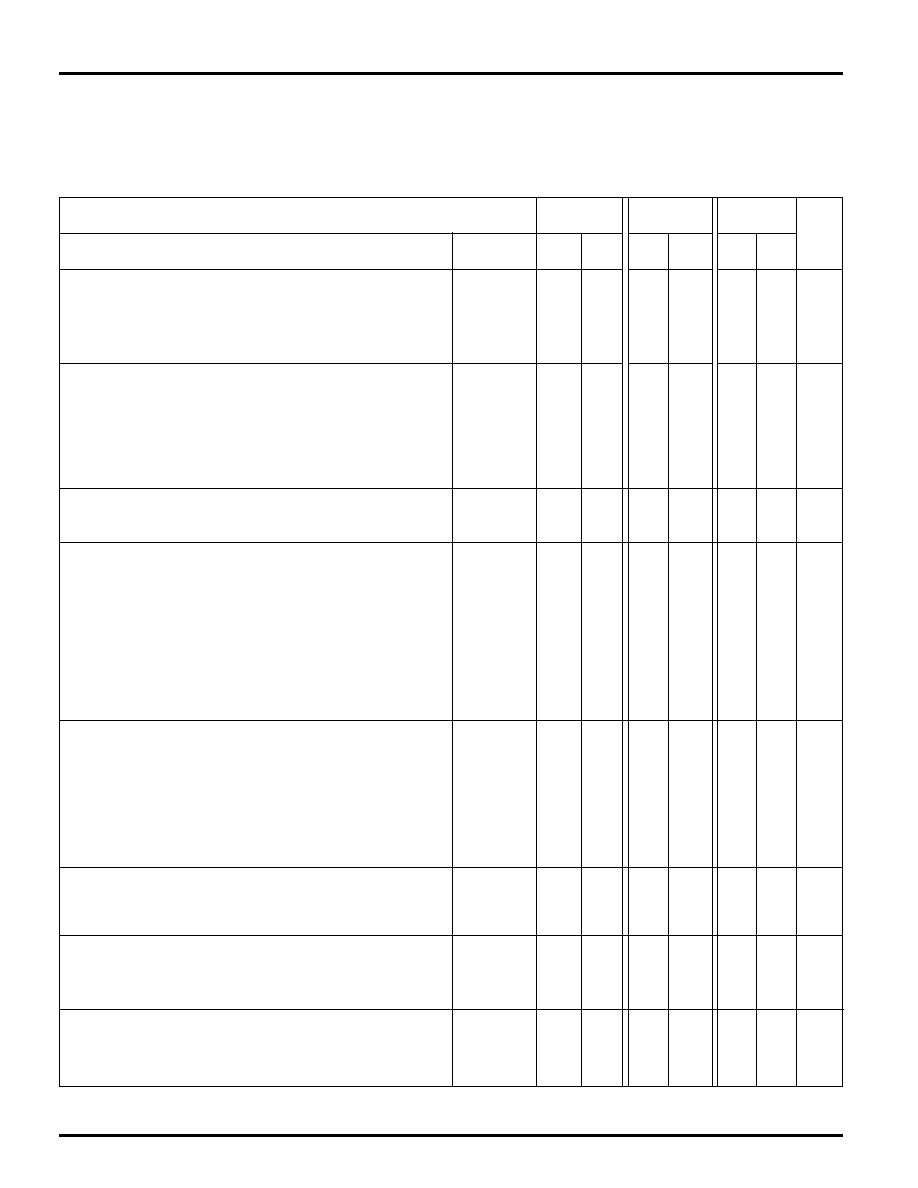

Speed Grade

-4

-3

-2

Description

Symbol

Min

Max

Min Max

Min Max Units

Combinatorial Delays

F/G inputs to X/Y outputs

T

ILO

2.0

ns

F/G inputs via H’ to X/Y outputs

T

IHO

3.6

ns

C inputs via H’ to X/Y outputs

T

HHO

2.9

ns

CLB Fast Carry Logic

Operand inputs (F1,F2,G1,G4) to COUT

T

OPCY

2.6

ns

Add/Subtract input (F3) to COUT

T

ASCY

4.4

ns

Initialization inputs (F1,F3) to COUT

T

INCY

1.7

ns

C

IN through function generators to X/Y outputs

T

SUM

3.3

ns

C

IN to COUT, bypass function generators.

T

BYP

0.7

ns

Sequential Delays

Clock K to outputs Q

T

CKO

2.4

ns

Set-up Time before Clock K

F/G inputs

T

ICK

2.3

ns

F/G inputs via H’

T

IHCK

4.0

ns

C inputs via H1

T

HHCK

3.3

ns

C inputs via DIN

T

DICK

1.9

ns

C inputs via EC

T

ECCK

2.6

ns

C inputs via S/R, going Low (inactive)

T

RCK

1.7

ns

C

IN

input via F'/G'

T

CCK

ns

C

IN

input via F'/G' and H'

T

CHCK

ns

Hold Time after Clock K

F/G inputs

T

CKI

0ns

F/G inputs via H’

T

CKIH

0ns

C inputs via H1

T

CKHH

0ns

C inputs via DIN

T

CKDI

0ns

C inputs via EC

T

CKEC

0ns

C inputs via S/R, going Low (inactive)

T

CKR

0ns

Clock

Clock High time

T

CH

4.0

ns

Clock Low time

T

CL

4.0

ns

Set/Reset Direct

Width (High)

T

RPW

4.0

ns

Delay from C inputs via S/R, going High to Q

T

RIO

4.0

ns

Master Set/Reset*

Width (High or Low)

T

MRW

18.9

ns

Delay from Global Set/Reset net to Q

T

MRQ

14.4

ns

CLB Switching Characteristic Guidelines

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100%

functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark timing

patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more detailed, more

precise, and more up-to-date timing information, use the values provided by the XACT timing calculator and used in the simulator.

*

Timing is based on the XC4005E. For other devices see XACT timing calculator.

相关PDF资料 |

PDF描述 |

|---|---|

| XC4013E-1VQ240M | XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-2BG240C | XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-2BG240I | XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-2BG240M | XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-2CB240C | XC4000E and XC4000X Series Field Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC4013E-3CB240C | 制造商:XILINX 制造商全称:XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-3CB240I | 制造商:XILINX 制造商全称:XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-3CB240M | 制造商:XILINX 制造商全称:XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-3HG240C | 制造商:XILINX 制造商全称:XILINX 功能描述:Programmable Gate Arrays |

| XC4013E-3HG240I | 制造商:XILINX 制造商全称:XILINX 功能描述:Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。