参数资料

| 型号: | XC4VFX60-11FFG672I |

| 厂商: | Xilinx Inc |

| 文件页数: | 8/9页 |

| 文件大小: | 0K |

| 描述: | IC FPGA VIRTEX-4 FX 60K 672-FBGA |

| 标准包装: | 1 |

| 系列: | Virtex®-4 FX |

| LAB/CLB数: | 6320 |

| 逻辑元件/单元数: | 56880 |

| RAM 位总计: | 4276224 |

| 输入/输出数: | 352 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 672-BBGA,FCBGA |

| 供应商设备封装: | 672-FCBGA(27x27) |

| 配用: | HW-V4-ML410-UNI-G-ND - EVALUATION PLATFORM VIRTEX-4 |

Virtex-4 Family Overview

DS112 (v3.1) August 30, 2010

Product Specification

8

R

Virtex-4 Documentation

Complete and up-to-date documentation of the Virtex-4

family of FPGAs is available on the Xilinx web site. In addi-

tion to the most recent Virtex-4 Family Overview, the follow-

ing files are also available for download:

This data sheet contains the DC and Switching Characteris-

tic specifications for the Virtex-4 family.

This guide includes chapters on:

Clocking Resources

Digital Clock Manager (DCM)

Phase-Matched Clock Dividers (PMCD)

Block RAM and FIFO memory

Configurable Logic Blocks (CLBs)

SelectIO Resources

SelectIO Logic Resources

Advanced SelectIO Logic Resources

This guide describes the DSP48 slice and includes refer-

ence designs for using DSP48 math functions and various

FIR filters.

This all-encompassing configuration guide includes chap-

ters on configuration interfaces (serial and SelectMAP), bit-

stream encryption, Boundary-Scan and JTAG configuration,

and reconfiguration techniques.

This specification includes the tables for device/package

combinations and maximum I/Os, pin definitions, pinout

tables, pinout diagrams, mechanical drawings, and thermal

specifications.

This guide describes PCB guidelines for the Virtex-4 family.

It covers SelectIO signaling, RocketIO signaling, power dis-

tribution systems, PCB breakout, and parts placement.

This guide describes the RocketIO Multi-Gigabit Transceiv-

ers available in the Virtex-4 FX family.

This guide describes the Embedded Tri-Mode Ethernet

Media Access Controller available in the Virtex-4 FX family.

This guide is updated to include the PowerPC 405 proces-

sor block available in the Virtex-4 FX family.

Revision History

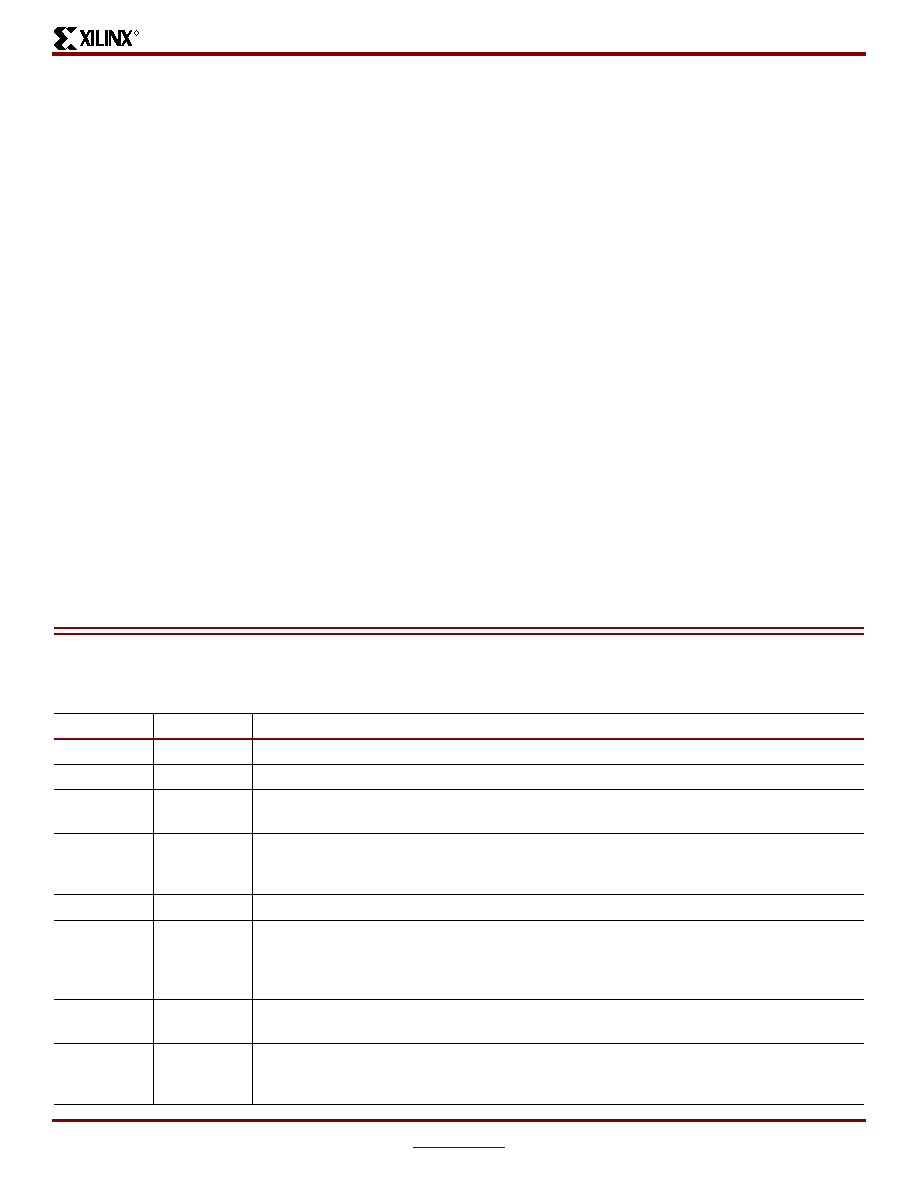

The following table shows the revision history for this document.

Date

Version

Revision

08/02/04

1.0

Initial Xilinx release. Printed Handbook version.

09/10/04

1.1

Typographical edits.

12/08/04

1.2

Removed System Monitor and ADC references.

Edited Ethernet MAC section.

03/26/05

1.3

Removed legacy CLB reference and typographical edits.

Edited serial transceiver sections.

In Table 2 added FFG Pb-Free packages.

06/17/05

1.4

Added note to Table 2 for SparseChevron pinouts.

02/10/06

1.5

Removed FCRAM-II support.

Added note 3 to Table 1.

Revised the CLB numbers for XC4VFX40 devices in Table 1.

Added stepping to order information example in Figure 1.

10/10/06

1.6

Changed maximum transceiver rate to 6.5 Gb/s.

Removed FF1760 package from Table 2.

01/23/07

2.0

Revision number jumped to 2.0 to correlate to data sheet (DS302) major revision.

Table 1: Corrected typo: XC4VFX40 number of slices = 18,624.

Table 2: Added column for FF676 package. Rewrote table footnotes.

相关PDF资料 |

PDF描述 |

|---|---|

| XC5VLX85-1FFG1153I | IC FPGA VIRTEX-5 85K 1153FBGA |

| XC5VLX85-1FF1153I | IC FPGA VIRTEX-5 85K 1153FBGA |

| EMC18DTEN | CONN EDGECARD 36POS .100 EYELET |

| EMC18DTEH | CONN EDGECARD 36POS .100 EYELET |

| XC5VFX70T-1FFG1136I | IC FPGA VIRTEX-5FX 70K 1136-FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC4VFX60-12FF1152C | 制造商:Xilinx 功能描述: |

| XC4VFX60-12FF672C | 制造商:Xilinx 功能描述: |

| XC4VFX60-12FF672CES4S | 制造商:Xilinx 功能描述: |

| XC4VFX60-12FFG1152CES5 | 制造商:Xilinx 功能描述: |

| XC4VFX60-12FFG672C | 制造商:Xilinx 功能描述: |

发布紧急采购,3分钟左右您将得到回复。