参数资料

| 型号: | XC4VLX25-10FFG676I |

| 厂商: | Xilinx Inc |

| 文件页数: | 2/9页 |

| 文件大小: | 0K |

| 描述: | IC FPGA VIRTEX-4 LX 25K 676-FBGA |

| 产品变化通告: | Virtex-4 LX25 FPGA Discontinuation 05/May/2010 |

| 标准包装: | 1 |

| 系列: | Virtex®-4 LX |

| LAB/CLB数: | 2688 |

| 逻辑元件/单元数: | 24192 |

| RAM 位总计: | 1327104 |

| 输入/输出数: | 448 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 676-BBGA,FCBGA |

| 供应商设备封装: | 676-FCBGA(27x27) |

| 配用: | 807-1004-ND - DAUGHTER CARD WITH VIRTEX-4 122-1523-ND - EVALUATION PLATFORM VIRTEX-4 |

Virtex-4 Family Overview

DS112 (v3.1) August 30, 2010

Product Specification

2

R

System Blocks Common to All Virtex-4 Families

Xesium Clock Technology

Up to twenty Digital Clock Manager (DCM) modules

-

Precision clock deskew and phase shift

-

Flexible frequency synthesis

-

Dual operating modes to ease performance trade-off

decisions

-

Improved maximum input/output frequency

-

Improved phase shifting resolution

-

Reduced output jitter

-

Low-power operation

-

Enhanced phase detectors

-

Wide phase shift range

Companion Phase-Matched Clock Divider (PMCD)

blocks

Differential clocking structure for optimized low-jitter

clocking and precise duty cycle

32 Global Clock networks

Regional I/O and Local clocks

Flexible Logic Resources

Up to 40% speed improvement over previous

generation devices

Up to 200,000 logic cells including:

-

Up to 178,176 internal registers with clock enable

(XC4VLX200)

-

Up to 178,176 look-up tables (LUTs)

-

Logic expanding multiplexers and I/O registers

Cascadable variable shift registers or distributed

memory capability

500 MHz XtremeDSP Slices

Dedicated 18-bit x 18-bit multiplier,

multiply-accumulator, or multiply-adder blocks

Optional pipeline stages for enhanced performance

Optional 48-bit accumulator for multiply accumulate

(MACC) operation

Integrated adder for complex-multiply or multiply-add

operation

Cascadeable Multiply or MACC

Up to 100% speed improvement over previous

generation devices.

500 MHz Integrated Block Memory

Up to 10 Mb of integrated block memory

Optional pipeline stages for higher performance

Multi-rate FIFO support logic

-

Full and Empty Flag support

-

Fully programmable AF and AE Flags

-

Synchronous/ Asynchronous Operation

Dual-port architecture

Independent read and write port width selection (RAM

only)

18 Kbit blocks (memory and parity/sideband memory

support)

Configurations from 16K x 1 to 512 x 36

(4K x 4 to 512 x 36 for FIFO operation)

Byte-write capability (connection to PPC405, etc.)

Dedicated cascade routing to form 32K x 1 memory

without using FPGA routing

Up to 100% speed improvement over previous

generation devices.

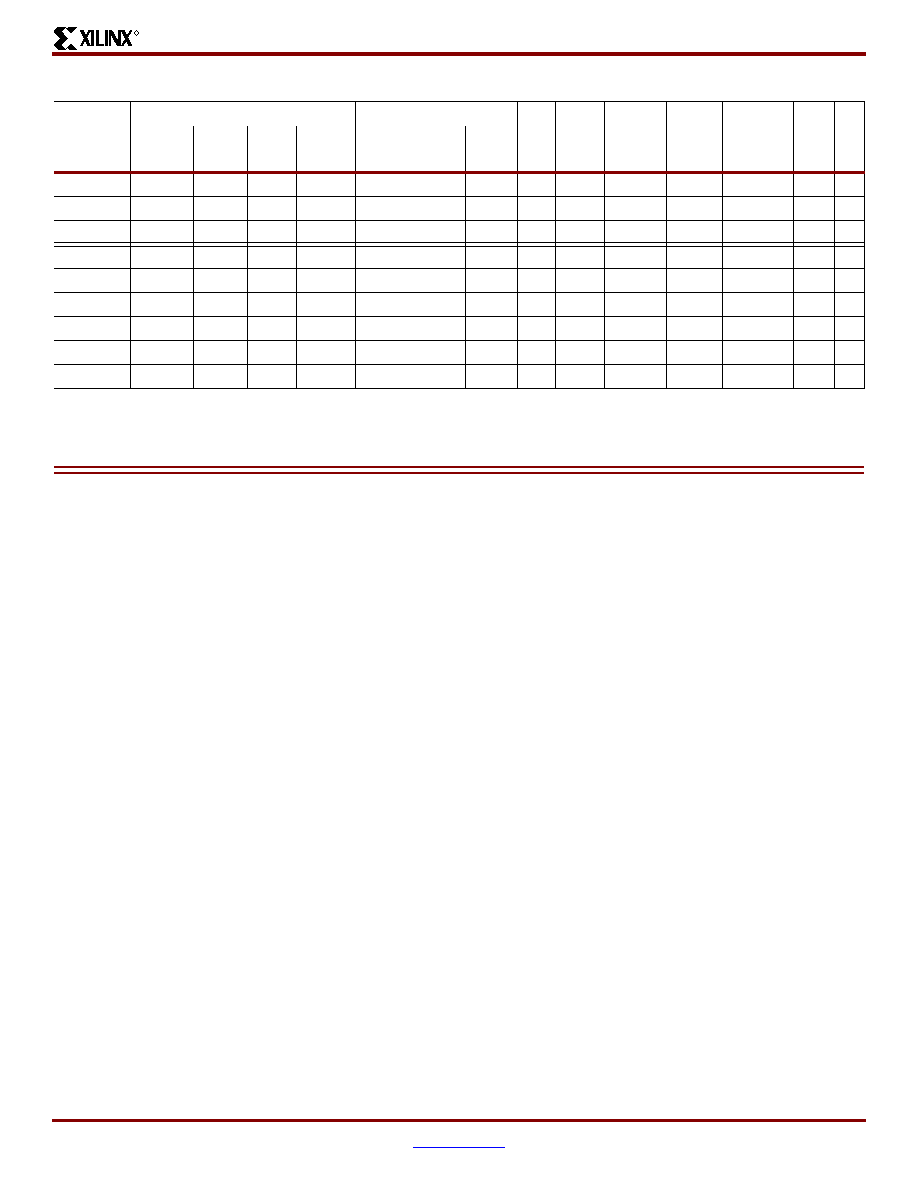

XC4VSX25

64 x 40

23,040

10,240

160

128

2,304

4

0

N/A

9

320

XC4VSX35

96 x 40

34,560

15,360

240

192

3,456

8

4

N/A

11

448

XC4VSX55

128 x 48

55,296

24,576

384

512

320

5,760

8

4

N/A

13

640

XC4VFX12

64 x 24

12,312

5,472

86

32

36

648

4

0

1

2

N/A

9

320

XC4VFX20

64 x 36

19,224

8,544

134

32

68

1,224

4

0

1

2

8

9

320

XC4VFX40

96 x 52

41,904

18,624

291

48

144

2,592

8

4

2

4

12

11

448

XC4VFX60

128 x 52

56,880

25,280

395

128

232

4,176

12

8

2

4

16

13

576

XC4VFX100

160 x 68

94,896

42,176

659

160

376

6,768

12

8

2

4

20

15

768

XC4VFX140

192 x 84

142,128

63,168

987

192

552

9,936

20

8

2

4

24

17

896

Notes:

1.

One CLB = Four Slices = Maximum of 64 bits.

2.

Each XtremeDSP slice contains one 18 x 18 multiplier, an adder, and an accumulator

3.

Some of the row/column array is used by the processors in the FX devices.

Table 1: Virtex-4 FPGA Family Members (Continued)

Device

Configurable Logic Blocks (CLBs)(1)

XtremeDSP

Slices(2)

Block RAM

DCMs PMCDs

PowerPC

Processor

Blocks

Ethernet

MACs

RocketIO

Transceiver

Blocks

Total

I/O

Banks

Max

User

I/O

Array(3)

Row x Col

Logic

Cells

Slices

Max

Distributed

RAM (Kb)

18 Kb

Blocks

Max

Block

RAM (Kb)

相关PDF资料 |

PDF描述 |

|---|---|

| IDT7133SA25J8 | IC SRAM 32KBIT 25NS 68PLCC |

| RMC18DTEF | CONN EDGECARD 36POS .100 EYELET |

| ASC65DRYN | CONN EDGECARD 130PS .100 DIP SLD |

| ASC65DRYH | CONN EDGECARD 130PS .100 DIP SLD |

| 4-1734248-0 | CONN FPC/ZIF 40POS 1MM VERT SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC4VLX25-10SF363C | 制造商:Xilinx 功能描述:FPGA VIRTEX-4 24192 CELLS 90NM 1.2V 363FCBGA - Trays |

| XC4VLX25-10SF363I | 功能描述:IC FPGA VIRTEX-4LX 363FCBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 LX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC4VLX25-10SFG363C | 功能描述:IC FPGA VIRTEX-4 24K 363-FCBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 LX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC4VLX25-10SFG363I | 功能描述:IC FPGA VIRTEX-4 LX 25K 363FCBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 LX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC4VLX25-11FF668C | 功能描述:IC FPGA VIRTEX-4 24K 668-FCBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-4 LX 产品变化通告:Step Intro and Pkg Change 11/March/2008 标准包装:1 系列:Virtex®-5 SXT LAB/CLB数:4080 逻辑元件/单元数:52224 RAM 位总计:4866048 输入/输出数:480 门数:- 电源电压:0.95 V ~ 1.05 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:1136-BBGA,FCBGA 供应商设备封装:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

发布紧急采购,3分钟左右您将得到回复。