参数资料

| 型号: | XC5VLX110-3FF676C |

| 厂商: | Xilinx Inc |

| 文件页数: | 58/91页 |

| 文件大小: | 0K |

| 描述: | IC FPGA VIRTEX-5 110K 676FBGA |

| 标准包装: | 1 |

| 系列: | Virtex®-5 LX |

| LAB/CLB数: | 8640 |

| 逻辑元件/单元数: | 110592 |

| RAM 位总计: | 4718592 |

| 输入/输出数: | 440 |

| 电源电压: | 0.95 V ~ 1.05 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 676-BBGA,FCBGA |

| 供应商设备封装: | 676-FCBGA(27x27) |

| 配用: | 568-5088-ND - BOARD DEMO DAC1408D750 HW-V5-ML523-UNI-G-ND - EVALUATION PLATFORM VIRTEX-5 HW-AFX-FF676-500-G-ND - BOARD DEV VIRTEX 5 FF676 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页当前第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页

Virtex-5 FPGA Data Sheet: DC and Switching Characteristics

DS202 (v5.3) May 5, 2010

Product Specification

61

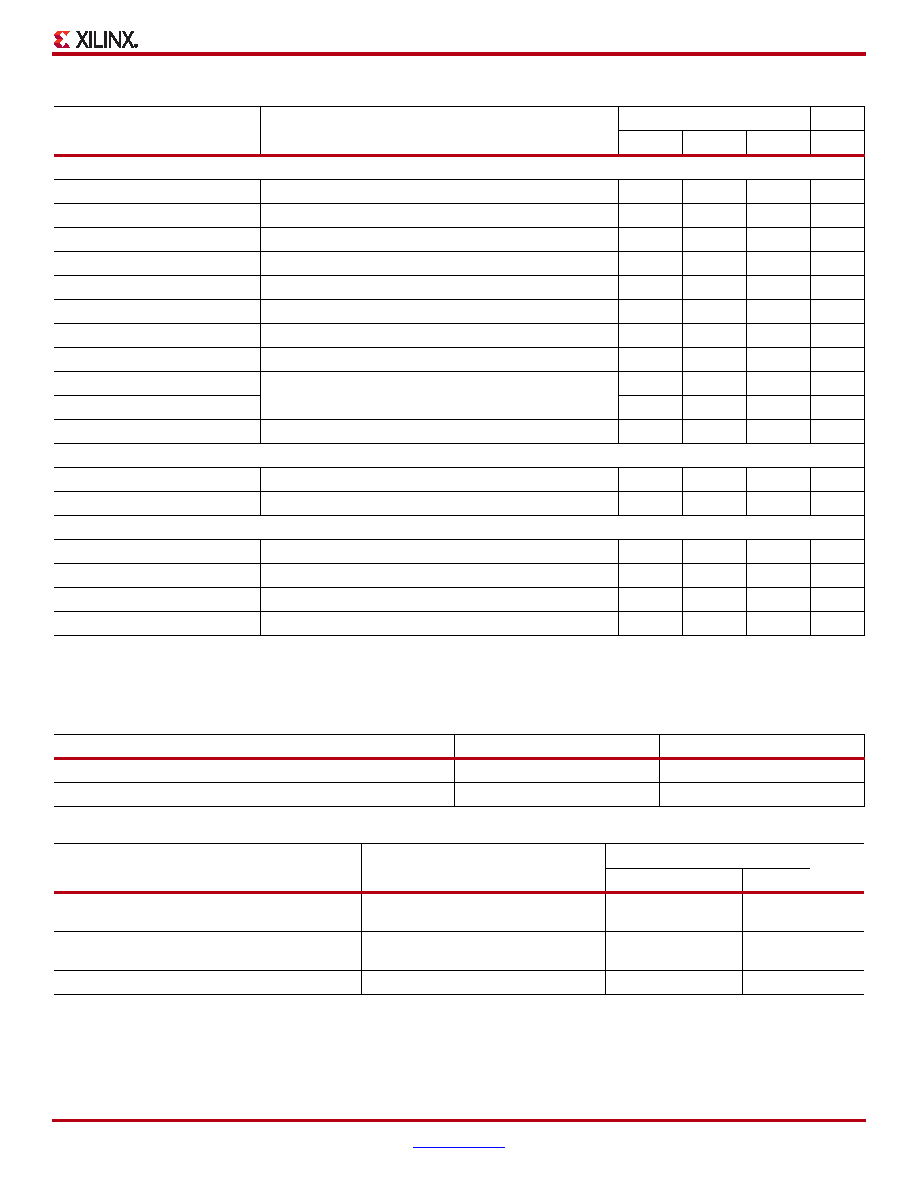

Table 81: Miscellaneous Timing Parameters

Symbol

Description

Speed Grade

-3

-2

-1

Units

Time Required to Achieve LOCK

TDLL_240

DLL output – Frequency range > 240 MHz (1)

80.00

s

TDLL_120_240

DLL output – Frequency range 120 - 240 MHz (1)

250.00

s

TDLL_60_120

DLL output – Frequency range 60 - 120 MHz (1)

900.00

s

TDLL_50_60

DLL output – Frequency range 50 - 60 MHz(1)

1300.00

s

TDLL_40_50

DLL output – Frequency range 40 - 50 MHz (1)

2000.00

s

TDLL_30_40

DLL output – Frequency range 30 - 40 MHz (1)

3600.00

s

TDLL_24_30

DLL output – Frequency range 24 - 30 MHz(1)

5000.00

s

TDLL_30

DLL output – Frequency range < 30 MHz (1)

5000.00

s

TFX_MIN

DFS outputs(2)

10.00

ms

TFX_MAX

10.00

ms

TDLL_FINE_SHIFT

Multiplication factor for DLL lock time with Fine Shift

2.00

Fine Phase Shifting

TRANGE_MS

Absolute shifting range in maximum speed mode

7.00

ns

TRANGE_MR

Absolute shifting range in maximum range mode

10.00

ns

Delay Lines

TTAP_MS_MIN

Tap delay resolution (Min) in maximum speed mode

7.00

ps

TTAP_MS_MAX

Tap delay resolution (Max) in maximum speed mode

30.00

ps

TTAP_MR_MIN

Tap delay resolution (Min) in maximum range mode

10.00

ps

TTAP_MR_MAX

Tap delay resolution (Max) in maximum range mode

40.00

ps

Notes:

1.

DLL Outputs are used in these instances to describe the outputs: CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV.

2.

DFS Outputs are used in these instances to describe the outputs: CLKFX and CLKFX180.

Table 82: Frequency Synthesis

Attribute

Min

Max

CLKFX_MULTIPLY

2

33

CLKFX_DIVIDE

1

32

Table 83: DCM Switching Characteristics

Symbol

Description

Speed Grade

Units

-3

-2

-1

TDMCCK_PSEN/ TDMCKC_PSEN

PSEN Setup/Hold

1.20

0.00

1.35

0.00

1.56

0.00

ns

TDMCCK_PSINCDEC/ TDMCKC_PSINCDEC

PSINCDEC Setup/Hold

1.20

0.00

1.35

0.00

1.56

0.00

ns

TDMCKO_PSDONE

Clock to out of PSDONE

1.00

1.12

1.30

ns

相关PDF资料 |

PDF描述 |

|---|---|

| XC5VLX110-2FFG676I | IC FPGA VIRTEX-5 110K 676FBGA |

| IDT71V124SA12TYG8 | IC SRAM 1MBIT 12NS 32SOJ |

| XC5VLX110-2FF676I | IC FPGA VIRTEX-5 110K 676FBGA |

| XCV1000E-7FG1156C | IC FPGA 1.8V C-TEMP 1156-FBGA |

| XCV1000E-6FG1156I | IC FPGA 1.8V I-TEMP 1156-FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC5VLX110-3FFG1153C | 功能描述:IC FPGA VIRTEX-5 110K 1153FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 LX 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC5VLX110-3FFG1760C | 功能描述:IC FPGA VIRTEX-5 110K 1760FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 LX 标准包装:24 系列:ECP2 LAB/CLB数:1500 逻辑元件/单元数:12000 RAM 位总计:226304 输入/输出数:131 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:208-BFQFP 供应商设备封装:208-PQFP(28x28) |

| XC5VLX110-3FFG676C | 功能描述:IC FPGA VIRTEX-5 110K 676FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 LX 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

| XC5VLX110T | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-5 Family Overview |

| XC5VLX110T-1FF1136C | 功能描述:IC FPGA VIRTEX-5 110K 1136FBGA RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Virtex®-5 LXT 产品变化通告:XC4000(E,L) Discontinuation 01/April/2002 标准包装:24 系列:XC4000E/X LAB/CLB数:100 逻辑元件/单元数:238 RAM 位总计:3200 输入/输出数:80 门数:3000 电源电压:4.5 V ~ 5.5 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:120-BCBGA 供应商设备封装:120-CPGA(34.55x34.55) |

发布紧急采购,3分钟左右您将得到回复。