参数资料

| 型号: | XC6SLX9-N3FTG256I |

| 厂商: | Xilinx Inc |

| 文件页数: | 5/11页 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-6 256PBGA |

| 标准包装: | 90 |

| 系列: | Spartan® 6 LX |

| LAB/CLB数: | 715 |

| 逻辑元件/单元数: | 9152 |

| RAM 位总计: | 589824 |

| 输入/输出数: | 186 |

| 电源电压: | 1.14 V ~ 1.26 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 256-LBGA |

| 供应商设备封装: | 256-FTBGA |

Spartan-6 Family Overview

DS160 (v2.0) October 25, 2011

Product Specification

3

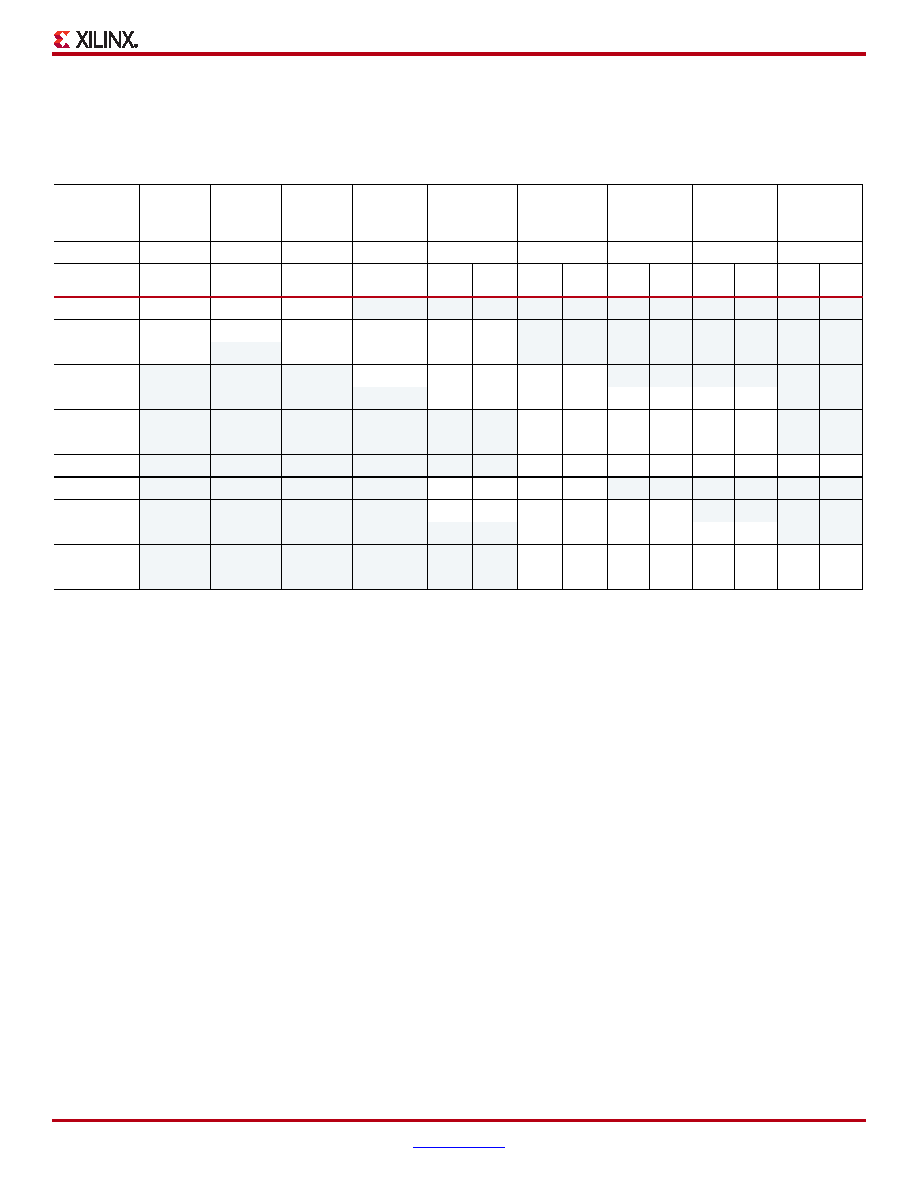

Spartan-6 FPGA Device-Package Combinations and Available I/Os

Spartan-6 FPGA package combinations with the available I/Os and GTP transceivers per package are shown in Table 2.

Due to the transceivers, the LX and LXT pinouts are not compatible.

Configuration

Spartan-6 FPGAs store the customized configuration data in SRAM-type internal latches. The number of configuration bits

is between 3 Mb and 33 Mb depending on device size and user-design implementation options. The configuration storage

is volatile and must be reloaded whenever the FPGA is powered up. This storage can also be reloaded at any time by pulling

the PROGRAM_B pin Low. Several methods and data formats for loading configuration are available.

Bit-serial configurations can be either master serial mode, where the FPGA generates the configuration clock (CCLK) signal,

or slave serial mode, where the external configuration data source also clocks the FPGA. For byte-wide configurations,

master SelectMAP mode generates the CCLK signal while slave SelectMAP mode receives the CCLK signal for the 8- and

16-bit-wide transfer. In master serial mode, the beginning of the bitstream can optionally switch the clocking source to an

external clock, which can be faster or more precise than the internal clock. The available JTAG pins use boundary-scan

protocols to load bit-serial configuration data.

Table 2: Spartan-6 Device-Package Combinations and Maximum Available I/Os

Package

CPG196(1)

TQG144(1)

CSG225(2)

FT(G)256(3)

CSG324

FG(G)484(3,4)

CSG484(4)

FG(G)676(3)

FG(G)900(3)

Body Size

(mm)

8x 8

20x20

13x13

17x17

15x15

23x23

19x19

27x 27

31x31

Pitch (mm)

0.5

0.8

1.0

0.8

1.0

0.8

1.0

Device

User I/O

GTPs

User

I/O

GTPs

User

I/O

GTPs

User

I/O

GTPs

User

I/O

GTPs

User

I/O

XC6SLX4

106

102

132

XC6SLX9

106

102

160

186

NA

200

XC6SLX16

106

160

186

NA

232

XC6SLX25

186

NA

226

NA

266

XC6SLX45

NA

218

NA

316

NA

320

NA

358

XC6SLX75

NA

280

NA

328

NA

408

XC6SLX100

NA

326

NA

338

NA

480

XC6SLX150

NA

338

NA

338

NA

498

NA

576

XC6SLX25T

2

190

2

250

XC6SLX45T

4

190

4

296

4

296

XC6SLX75T

4

268

4

292

8

348

XC6SLX100T

4

296

4

296

8

376

8

498

XC6SLX150T

4

296

4

296

8

396

8

540

Notes:

1.

There is no memory controller on the devices in these packages.

2.

Memory controller block support is x8 on the XC6SLX9 and XC6SLX16 devices in the CSG225 package. There is no memory controller in the

XC6SLX4.

3.

These devices are available in both Pb and Pb-free (additional G) packages as standard ordering options.

4.

These packages support two of the four memory controllers in the XC6SLX75, XC6SLX75T, XC6SLX100, XC6SLX100T, XC6SLX150, and

XC6SLX150T devices.

相关PDF资料 |

PDF描述 |

|---|---|

| XC6SLX9-N3CSG225I | IC FPGA SPARTAN-6 225CSBGA |

| RSA50DTMD-S664 | CONN EDGECARD 100PS R/A .125 SLD |

| XC6SLX9-2FT256I | IC FPGA SPARTAN 6 256FTGBGA |

| XC6SLX9-L1FTG256C | IC FPAG SPARTAN 6 9K 256FTGBGA |

| 93C66C-I/SN | IC EEPROM 4KBIT 3MHZ 8SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC6T644 | 制造商:Omron Electronic Components LLC 功能描述:CONN ACC SR - Bulk 制造商:Omron Electronic Components LLC 功能描述:CONNECTR 64POS STRAIN RELIEF DIN |

| XC6T-644 | 功能描述:DIN 41612 连接器 Connector RoHS:否 制造商:HARTING 系列:har-bus 64 产品类型:Plugs 排数:5 位置/触点数量:160 安装角:Right 类型:Shrouded Header 端接类型:Solder 外壳材料: 触点材料: 触点电镀: |

| XC6VCX130T | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-6 CXT Family Data Sheet |

| XC6VCX130T-1FF1156C | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 128000 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA 600 I/O 1156FCBGA 制造商:Xilinx 功能描述:IC FPGA VIRTEX 6 128K 1156BGA |

| XC6VCX130T-1FF1156I | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 128000 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA 600 I/O 1156FCBGA 制造商:Xilinx 功能描述:IC FPGA VIRTEX 6 128K 1156BGA |

发布紧急采购,3分钟左右您将得到回复。