- 您现在的位置:买卖IC网 > PDF目录19665 > XCR3384XL-12PQ208C (Xilinx Inc)IC CPLD 3.3V ZERO PWR 208-PQFP PDF资料下载

参数资料

| 型号: | XCR3384XL-12PQ208C |

| 厂商: | Xilinx Inc |

| 文件页数: | 11/12页 |

| 文件大小: | 0K |

| 描述: | IC CPLD 3.3V ZERO PWR 208-PQFP |

| 标准包装: | 24 |

| 系列: | CoolRunner XPLA3 |

| 可编程类型: | 系统内可编程(最少 1K 次编程/擦除循环) |

| 最大延迟时间 tpd(1): | 10.8ns |

| 电压电源 - 内部: | 3 V ~ 3.6 V |

| 逻辑元件/逻辑块数目: | 24 |

| 宏单元数: | 384 |

| 门数: | 9000 |

| 输入/输出数: | 172 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 208-BFQFP |

| 供应商设备封装: | 208-PQFP(28x28) |

| 包装: | 托盘 |

| 其它名称: | XCR3384XL12PQ208C |

CoolRunner XPLA3 CPLD

8

DS012 (v2.5) May 26, 2009

Product Specification

R

3V, In-System Programming (ISP)

CoolRunner XPLA3 CPLDs allow for 3V, in-system pro-

gramming/reprogramming of its EEPROM cells via a JTAG

interface. An on-chip charge pump eliminates the need for

externally provided super-voltages. This allows program-

ming on the circuit board using only the 3V supply required

by the device for normal operation. The ISP commands

implemented in CoolRunner XPLA3 CPLDs are specified in

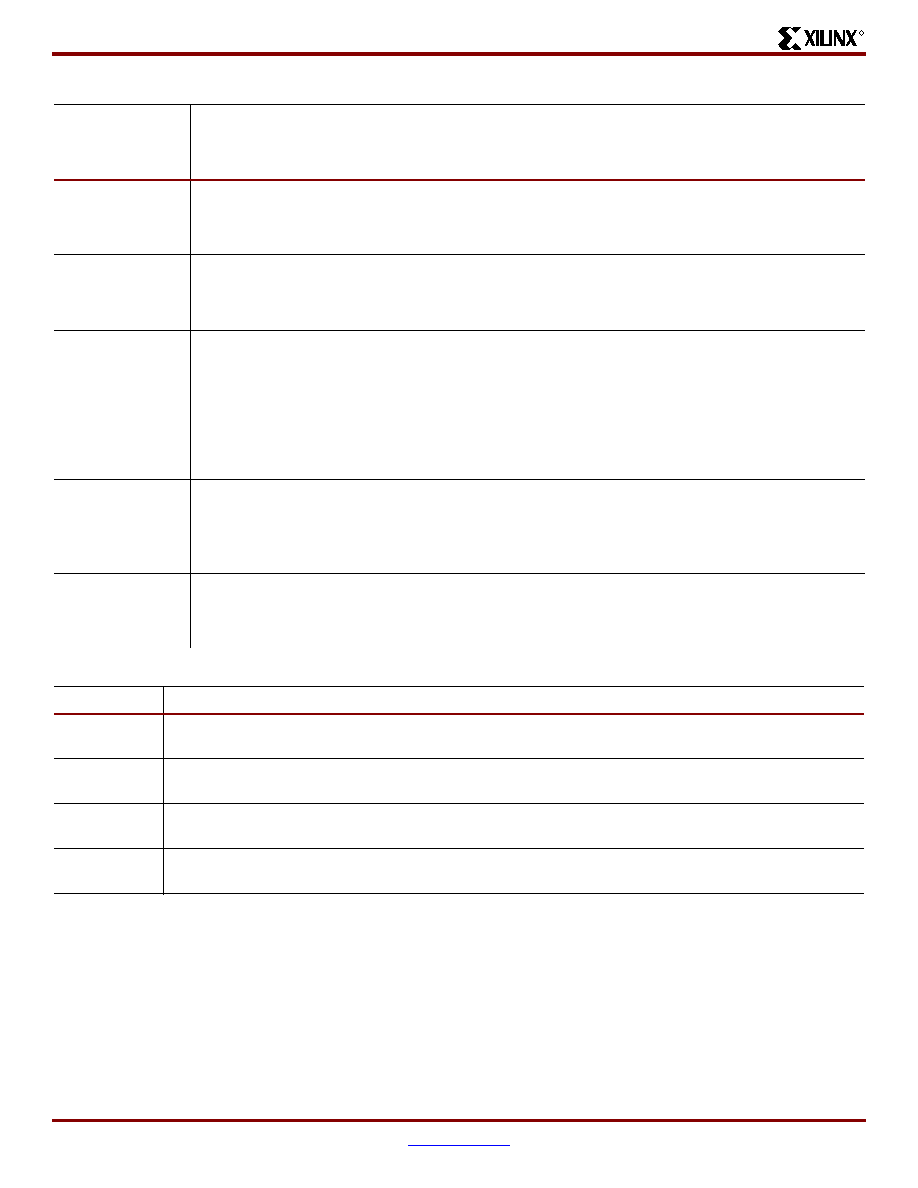

Table 4: XPLA3 Low-level JTAG Boundary-scan Commands

Instruction

(Instruction

Code)

Register Used

Description

Sample/Preload

(00010)

Boundary-scan

Register

The mandatory Sample/Preload instruction allows a snapshot of the normal operation of the

component to be taken and examined. It also allows data values to be loaded into the latched parallel

outputs of the Boundary-scan Shift Register prior to selection of the other boundary-scan test

instructions.

Extest

(00000)

Boundary-scan

Register

The mandatory Extest instruction allows testing of off-chip circuitry and board level interconnections.

Data is typically loaded onto the latched parallel outputs of Boundary-scan Shift Register using the

Sample/Preload instruction prior to selection of the Extest instruction.

Bypass

(11111)

Bypass Register

Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass

synchronously through the selected device to adjacent devices during normal device operation. The

Bypass instruction can be entered by holding TDI at a constant High value and completing an

Instruction-scan cycle.

Idcode

(00001)

Boundary-scan

Register

Selects the Idcode register and places it between TDI and TDO, allowing the Idcode to be serially

shifted out of TDO. The Idcode instruction permits blind interrogation of the components assembled

onto a printed circuit board. Thus, in circumstances where the component population can vary, it is

possible to determine what components exist in a product.

High-Z

(00101)

Bypass Register

The High-Z instruction places the component in a state which all of its system logic outputs are placed

in an inactive drive state (e.g., high impedance). In this state, an in-circuit test system can drive

signals onto the connections normally driven by a component output without incurring the risk of

damage to the component. The High-Z instruction also forces the Bypass Register between TDI and

TDO.

Intest

(00011)

Boundary-scan

Register

The Intest instruction selects the boundary scan register prior to applying tests to the logic core of the

device. This permits testing of on-chip system logic while the component is already on the board.

Table 5: JTAG Pin Description

Pin

Name

Description

TCK

Test Clock Input

Clock pin to shift the serial data and instructions in and out of the TDI and TDO pins,

respectively.

TMS

Test Mode Select

Serial input pin selects the JTAG instruction mode. TMS should be driven High during

user mode operation.

TDI

Test Data Input

Serial input pin for instructions and test data. Data is shifted in on the rising edge of

TCK.

TDO

Test Data Output

Serial output pin for instructions and test data. Data is shifted out on the falling edge

of TCK. The signal is 3-stated if data is not being shifted out of the device.

相关PDF资料 |

PDF描述 |

|---|---|

| GCC08DCSH | CONN EDGECARD 16POS DIP .100 SLD |

| DS1624S+ | IC THERM/EEPROM DIG 256BYT 8SOIC |

| XC2C512-10FTG256I | IC CR-II CPLD 512MCELL 256-FTBGA |

| PQ1L503M2SP | IC REG LDO 5V .3A SOT-89 |

| TAJT107M002RNJ | CAP TANT 100UF 2.5V 20% 1210 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCR3384XL-12PQ208I | 功能描述:IC CPLD 3.3V ZERO PWR 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - CPLD(复杂可编程逻辑器件) 系列:CoolRunner XPLA3 标准包装:40 系列:ispMACH® 4000C 可编程类型:系统内可编程 最大延迟时间 tpd(1):5.0ns 电压电源 - 内部:1.65 V ~ 1.95 V 逻辑元件/逻辑块数目:32 宏单元数:512 门数:- 输入/输出数:128 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:176-LQFP 供应商设备封装:176-TQFP(24x24) 包装:托盘 |

| XCR3384XL-12PQG208C | 制造商:Xilinx 功能描述:XLXXCR3384XL-12PQG208C XPLA3 384 MACROCE 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 9K GATES 384 MCRCLLS 100MHZ COMM 0.35U - Trays |

| XCR3384XL-12PQG208I | 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 9K GATES 384 MCRCLLS 100MHZ IND 0.35UM - Trays |

| XCR3384XL-12TQ144C | 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 9K GATES 384 MCRCLLS 100MHZ 0.35UM 3.3 - Trays |

| XCR3384XL-12TQ144I | 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 9K GATES 384 MCRCLLS 100MHZ 0.35UM 3.3 - Trays |

发布紧急采购,3分钟左右您将得到回复。