- 您现在的位置:买卖IC网 > PDF目录300150 > XCS20-3VQ208C (Xilinx, Inc.) Spartan and Spartan-XL Families Field Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | XCS20-3VQ208C |

| 厂商: | Xilinx, Inc. |

| 英文描述: | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| 中文描述: | 斯巴达和Spartan - xL的家庭现场可编程门阵列 |

| 文件页数: | 59/82页 |

| 文件大小: | 863K |

| 代理商: | XCS20-3VQ208C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

Spartan and Spartan-XL Families Field Programmable Gate Arrays

62

DS060 (v1.6) September 19, 2001

1-800-255-7778

Product Specification

R

Pin Descriptions

There are three types of pins in the Spartan/XL devices:

Permanently dedicated pins

User I/O pins that can have special functions

Unrestricted user-programmable I/O pins.

Before and during configuration, all outputs not used for the

configuration process are 3-stated with the I/O pull-up resis-

tor network activated. After configuration, if an IOB is

unused it is configured as an input with the I/O pull-up resis-

tor network remaining activated.

Any user I/O can be configured to drive the Global

Set/Reset net GSR or the global three-state net GTS. See

Global Signals: GSR and GTS, page 20 for more informa-

tion.

Device pins for Spartan/XL devices are described in

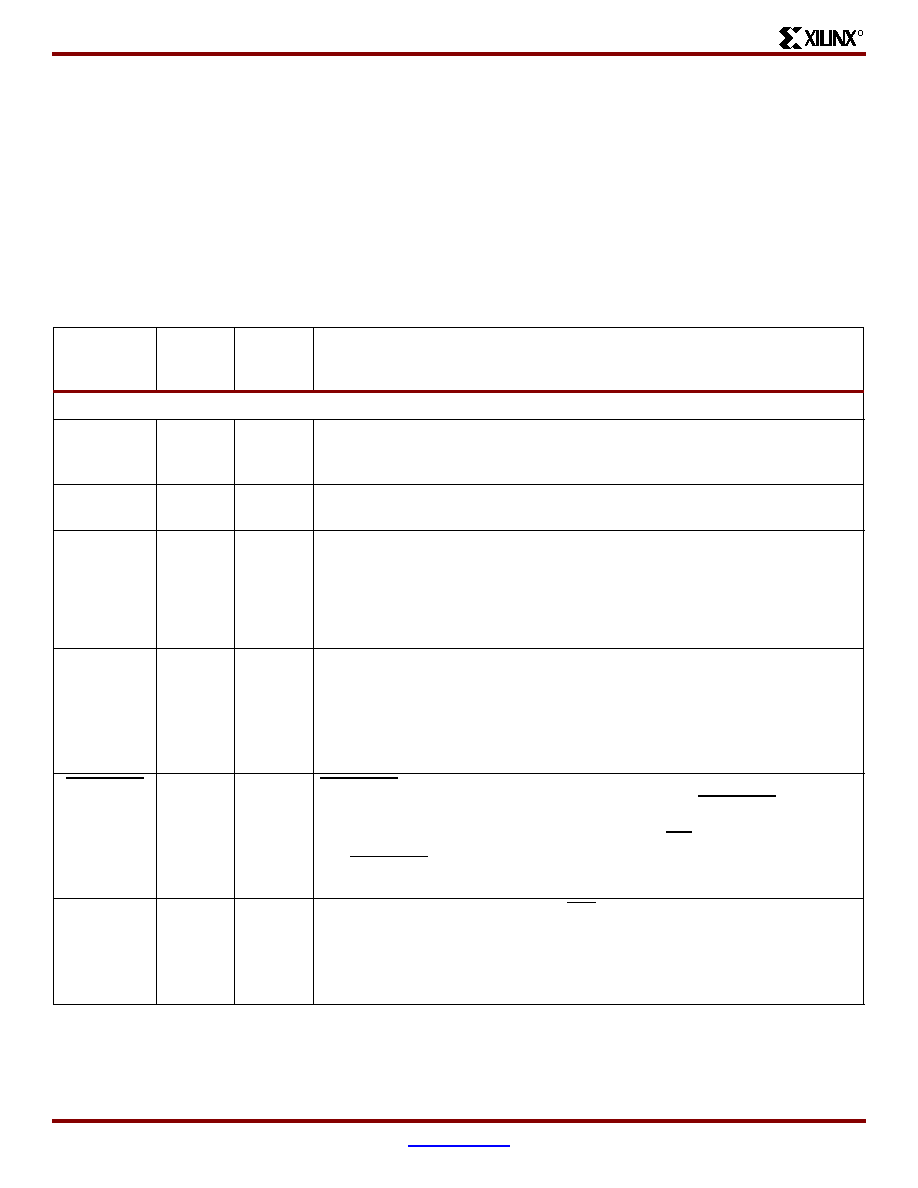

Table 18: Pin Descriptions

Pin Name

I/O

During

Config.

I/O After

Config.

Pin Description

Permanently Dedicated Pins

VCC

X

Eight or more (depending on package) connections to the nominal +5V supply

voltage (+3.3V for Spartan-XL devices). All must be connected, and each must be

decoupled with a 0.01 –0.1

F capacitor to Ground.

GND

X

Eight or more (depending on package type) connections to Ground. All must be

connected.

CCLK

I or O

I

During configuration, Configuration Clock (CCLK) is an output in Master mode and

is an input in Slave mode. After configuration, CCLK has a weak pull-up resistor

and can be selected as the Readback Clock. There is no CCLK High or Low time

restriction on Spartan/XL devices, except during Readback. See Violating the

for an explanation of this exception.

DONE

I/O

O

DONE is a bidirectional signal with an optional internal pull-up resistor. As an

open-drain output, it indicates the completion of the configuration process. As an

input, a Low level on DONE can be configured to delay the global logic initialization

and the enabling of outputs.

The optional pull-up resistor is selected as an option in the program that creates

the configuration bitstream. The resistor is included by default.

PROGRAM

I

PROGRAM is an active Low input that forces the FPGA to clear its configuration

memory. It is used to initiate a configuration cycle. When PROGRAM goes High,

the FPGA finishes the current clear cycle and executes another complete clear

cycle, before it goes into a WAIT state and releases INIT.

The PROGRAM pin has a permanent weak pull-up, so it need not be externally

pulled up to VCC.

MODE

(Spartan)

M0, M1

(Spartan-XL)

I

X

The Mode input(s) are sampled after INIT goes High to determine the

configuration mode to be used.

During configuration, these pins have a weak pull-up resistor. For the most popular

configuration mode, Slave Serial, the mode pins can be left unconnected. For

Master Serial mode, connect the Mode/M0 pin directly to system ground.

相关PDF资料 |

PDF描述 |

|---|---|

| XCS20-3VQ208I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3VQ240C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3VQ240I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3VQ256C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3VQ256I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCS20-3VQ208I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3VQ240C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3VQ240I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3VQ256C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20-3VQ256I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。