- 您现在的位置:买卖IC网 > PDF目录300158 > XCS40-3TQ256C (Xilinx, Inc.) Spartan and Spartan-XL Families Field Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | XCS40-3TQ256C |

| 厂商: | Xilinx, Inc. |

| 英文描述: | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| 中文描述: | 斯巴达和Spartan - xL的家庭现场可编程门阵列 |

| 文件页数: | 29/82页 |

| 文件大小: | 863K |

| 代理商: | XCS40-3TQ256C |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

Spartan and Spartan-XL Families Field Programmable Gate Arrays

DS060 (v1.6) September 19, 2001

Product Specification

1-800-255-7778

R

Configuration

The 0010 preamble code indicates that the following 24 bits

represent the length count for serial modes. The length

count is the total number of configuration clocks needed to

load the complete configuration data. (Four additional con-

figuration clocks are required to complete the configuration

process, as discussed below.) After the preamble and the

length count have been passed through to any device in the

daisy chain, its DOUT is held High to prevent frame start

bits from reaching any daisy-chained devices. In Spar-

tan-XL Express mode, the length count bits are ignored,

and DOUT is held Low, to disable the next device in the

pseudo daisy chain.

A specific configuration bit, early in the first frame of a mas-

ter device, controls the configuration-clock rate and can

increase it by a factor of eight. Therefore, if a fast configura-

tion clock is selected by the bitstream, the slower clock rate

is used until this configuration bit is detected.

Each frame has a start field followed by the frame-configu-

ration data bits and a frame error field. If a frame data error

is detected, the FPGA halts loading, and signals the error by

pulling the open-drain INIT pin Low. After all configuration

frames have been loaded into an FPGA using a serial

mode, DOUT again follows the input data so that the

remaining data is passed on to the next device. In

Spartan-XL Express mode, when the first device is fully pro-

grammed, DOUT goes High to enable the next device in the

chain.

Delaying Configuration After Power-Up

There are two methods of delaying configuration after

power-up: put a logic Low on the PROGRAM input, or pull

the bidirectional INIT pin Low, using an open-collector

(open-drain) driver. (See Figure 30.)

A Low on the PROGRAM input is the more radical

approach, and is recommended when the power-supply rise

time is excessive or poorly defined. As long as PROGRAM

is Low, the FPGA keeps clearing its configuration memory.

When PROGRAM goes High, the configuration memory is

cleared one more time, followed by the beginning of config-

uration, provided the INIT input is not externally held Low.

Note that a Low on the PROGRAM input automatically

forces a Low on the INIT output. The Spartan/XL PRO-

GRAM pin has a permanent weak pull-up. Avoid holding

PROGRAM Low for more than 500

s.

Using an open-collector or open-drain driver to hold INIT

Low before the beginning of configuration causes the FPGA

to wait after completing the configuration memory clear

operation. When INIT is no longer held Low externally, the

device determines its configuration mode by capturing the

state of the Mode pins, and is ready to start the configura-

tion process. A master device waits up to an additional

300

s to make sure that any slaves in the optional daisy

chain have seen that INIT is High.

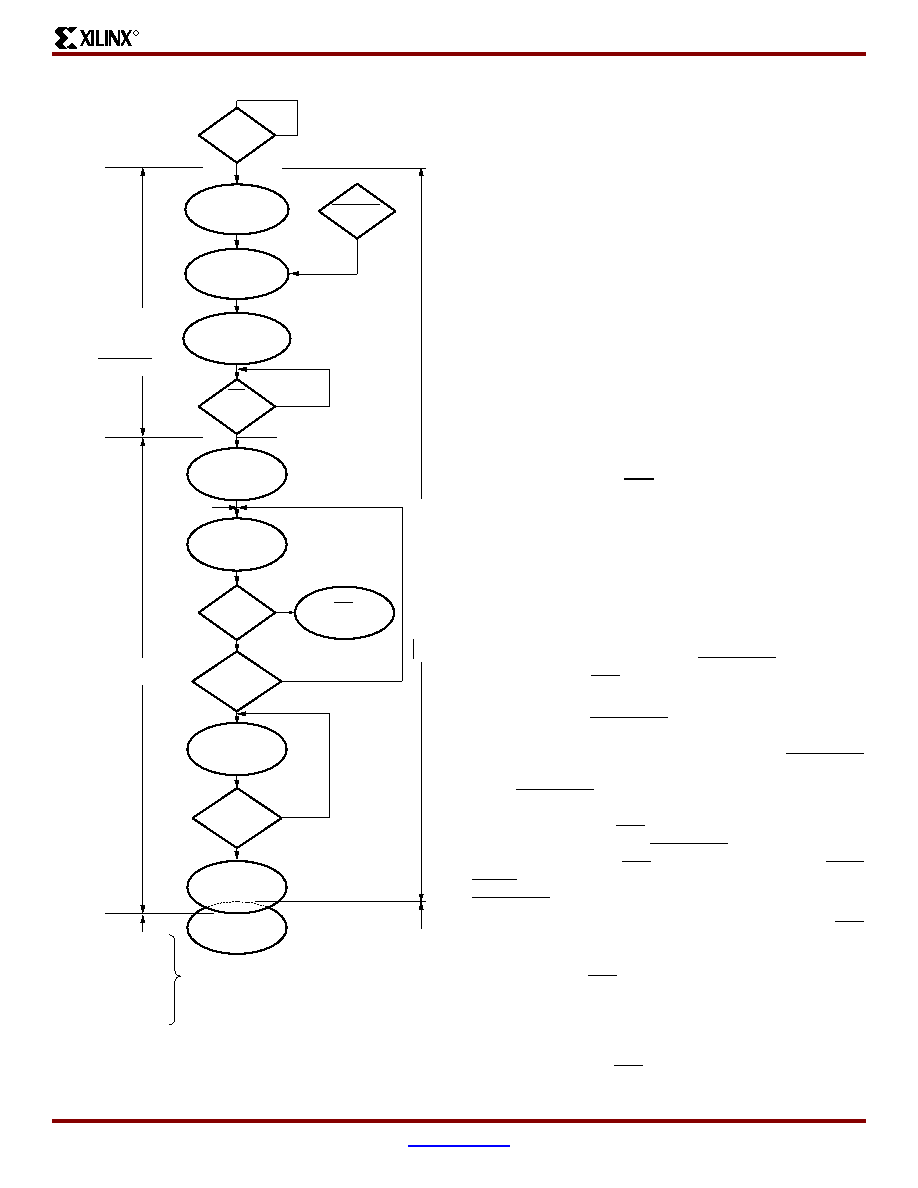

Figure 30: Power-up Configuration Sequence

INIT

High? if

Master

Sample

Mode Line

Load One

Configuration

Data Frame

Frame

Error

Pass

Configuration

Data to DOUT

VCC

Valid

No

Yes

No

Yes

Operational

Start-Up

Sequence

No

Yes

~1.3

s per Frame

Master Delays Before

Sampling Mode Line

Master CCLK

Goes Active

F

Pull INIT Low

and Stop

DS060_30_080400

EXTEST*

SAMPLE/PRELOAD

BYPASS

CONFIGURE*

(* if PROGRAM = High)

SAMPLE/PRELOAD

BYPASS

EXTEST

SAMPLE PRELOAD

BYPASS

USER 1

USER 2

CONFIGURE

READBACK

If Boundary Scan

is Selected

Config-

uration

memory

Full

CCLK

Count Equals

Length

Count

Completely Clear

Configuration Memory

Once More

LDC

Output

=

L,

HDC

Output

=

H

Boundary Scan

Instructions

Available:

I/O

Active

Keep Clearing

Configuration

Memory

Test MODE, Generate

One Time-Out Pulse

of 16 or 64 ms

PROGRAM

= Low

No

Yes

相关PDF资料 |

PDF描述 |

|---|---|

| XCS40-3TQ256I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3TQ280C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3TQ280I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3TQ84C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3TQ84I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCS40-3TQ256I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3TQ280C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3TQ280I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3TQ84C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-3TQ84I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。