- 您现在的位置:买卖IC网 > PDF目录16501 > XR16M564IV80-0B-EB (Exar Corporation)EVAL BOARD FOR XR16M564-B 80LQFP PDF资料下载

参数资料

| 型号: | XR16M564IV80-0B-EB |

| 厂商: | Exar Corporation |

| 文件页数: | 4/55页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR16M564-B 80LQFP |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页

XR16M564/564D

12

1.62V TO 3.63V QUAD UART WITH 32-BYTE FIFO

REV. 1.0.0

2.4

Channels A-D Internal Registers

Each UART channel in the M564 has a set of enhanced registers for controlling, monitoring and data loading

and unloading. The configuration register set is compatible to those already available in the standard single

16C550. These registers function as data holding registers (THR/RHR), interrupt status and control registers

(ISR/IER), a FIFO control register (FCR), receive line status and control registers (LSR/LCR), modem status

and control registers (MSR/MCR), programmable data rate (clock) divisor registers (DLL/DLM/DLD), and a

user accessible scratchpad register (SPR).

Beyond the general 16C550 features and capabilities, the M564 offers enhanced feature registers (EFR, Xon/

Xoff 1, Xon/Xoff 2)

that provide automatic RTS and CTS hardware flow control and automatic Xon/Xoff

software flow control.

All the register functions are discussed in full detail later

2.5

INT Ouputs for Channels A-D

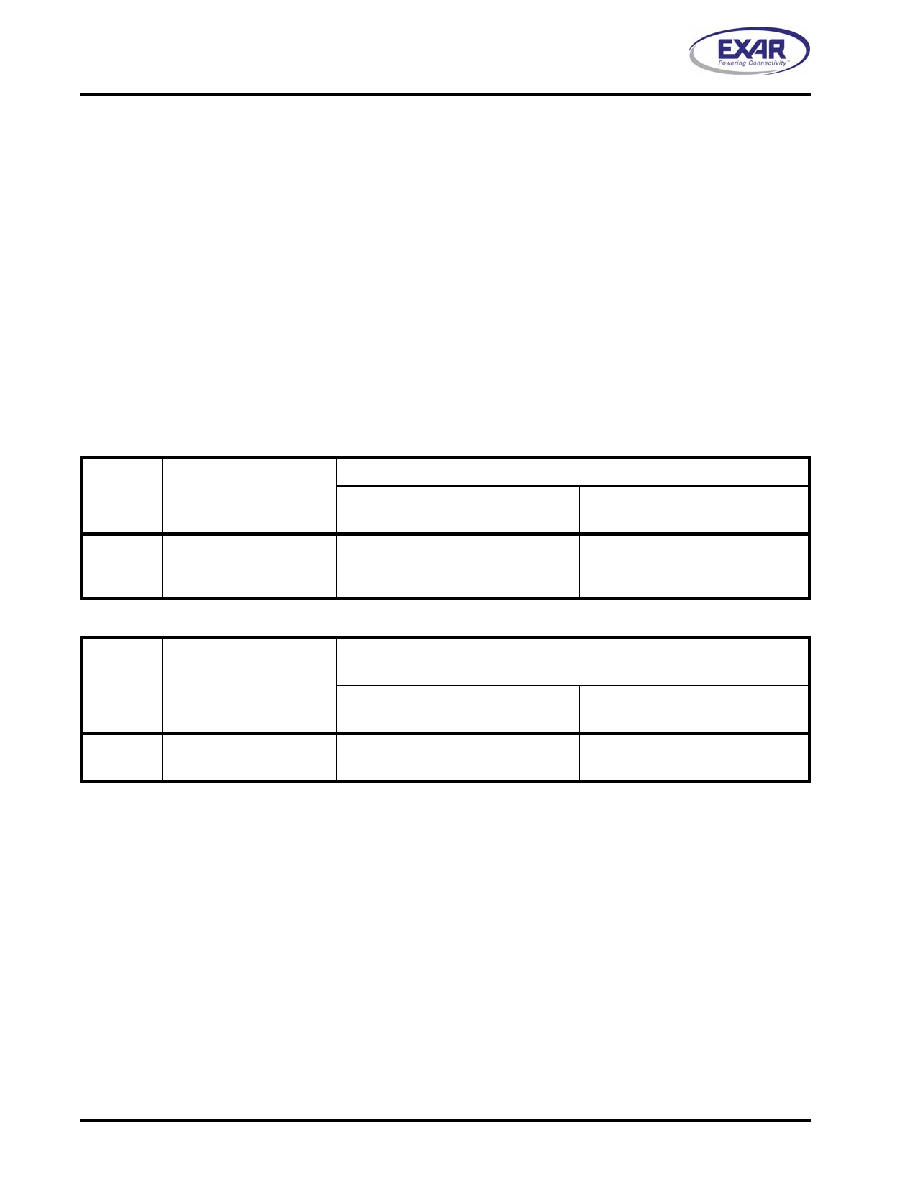

The interrupt outputs change according to the operating mode and enhanced features setup. Table 3 and 4

2.6

DMA Mode

The device does not support direct memory access. The DMA Mode (a legacy term) in this document does not

mean “direct memory access” but refers to data block transfer operation. The DMA mode affects the state of

the RXRDY# A-D and TXRDY# A-D output pins. The transmit and receive FIFO trigger levels provide

additional flexibility to the user for block mode operation. The LSR bits 5-6 provide an indication when the

transmitter is empty or has an empty location(s) for more data. The user can optionally operate the transmit

and receive FIFO in the DMA mode (FCR bit-3 = 1). When the transmit and receive FIFOs are enabled and the

DMA mode is disabled (FCR bit-3 = 0), the M564 is placed in single-character mode for data transmit or

receive operation. When DMA mode is enabled (FCR bit-3 = 1), the user takes advantage of block mode

TABLE 3: INT PIN OPERATION FOR TRANSMITTER FOR CHANNELS A-D

FCR BIT-0 = 0

(FIFO DISABLED)

FCR BIT-0 = 1 (FIFO ENABLED)

FCR Bit-3 = 0

(DMA Mode Disabled)

FCR Bit-3 = 1

(DMA Mode Enabled)

INT Pin

LOW = a byte in THR

HIGH = THR empty

LOW = FIFO above trigger level

HIGH = FIFO below trigger level or

FIFO empty

LOW = FIFO above trigger level

HIGH = FIFO below trigger level or

FIFO empty

TABLE 4: INT PIN OPERATION FOR RECEIVER FOR CHANNELS A-D

FCR BIT-0 = 0

(FIFO DISABLED)

FCR BIT-0 = 1 (FIFO ENABLED)

FCR Bit-3 = 0

(DMA Mode Disabled)

FCR Bit-3 = 1

(DMA Mode Enabled)

INT Pin

LOW = no data

HIGH = 1 byte

LOW = FIFO below trigger level

HIGH = FIFO above trigger level

LOW = FIFO below trigger level

HIGH = FIFO above trigger level

相关PDF资料 |

PDF描述 |

|---|---|

| H3AKH-5018M | IDC CABLE - HSC50H/AE50M/HPK50H |

| M1TXK-3036J | IDC CABLE - MSD30K/MC34G/X |

| RBC17DRYS | CONN EDGECARD 34POS DIP .100 SLD |

| H3KKH-1606M | IDC CABLE - HPK16H/AE16M/HPK16H |

| 1906014-7 | CA 2.0MM OFNR 50/125,LC SEC YEL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR16M564IV80-F | 功能描述:UART 接口集成电路 UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR16M570 | 制造商:EXAR 制造商全称:EXAR 功能描述:1.62V TO 3.63V HIGH PERFORMANCE UART WITH 16-BYTE FIFO |

| XR16M570IB25 | 制造商:EXAR 制造商全称:EXAR 功能描述:1.62V TO 3.63V HIGH PERFORMANCE UART WITH 16-BYTE FIFO |

| XR16M570IB25-0C-EB | 功能描述:界面开发工具 Eval Board for XR16M570IB25 Series RoHS:否 制造商:Bourns 产品:Evaluation Boards 类型:RS-485 工具用于评估:ADM3485E 接口类型:RS-485 工作电源电压:3.3 V |

| XR16M570IB25-F | 功能描述:UART 接口集成电路 1.8 HIGH PERFORMANCE UART W/16 RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。