- 您现在的位置:买卖IC网 > PDF目录16606 > XR16M890IM48-0C-EB (Exar Corporation)BOARD EVAL XR16M890IM48 PDF资料下载

参数资料

| 型号: | XR16M890IM48-0C-EB |

| 厂商: | Exar Corporation |

| 文件页数: | 5/63页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL XR16M890IM48 |

| 产品培训模块: | XR21V141x Full-Speed USB UART Family UARTs with Integrated Level Shifters |

| 标准包装: | 1 |

| 主要目的: | 接口,UART |

| 嵌入式: | 否 |

| 已用 IC / 零件: | XR16M890IM48 |

| 已供物品: | 板 |

| 其它名称: | 1016-1607 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页

�� �

�

�

�XR16M890�

�REV.� 1.0.0�

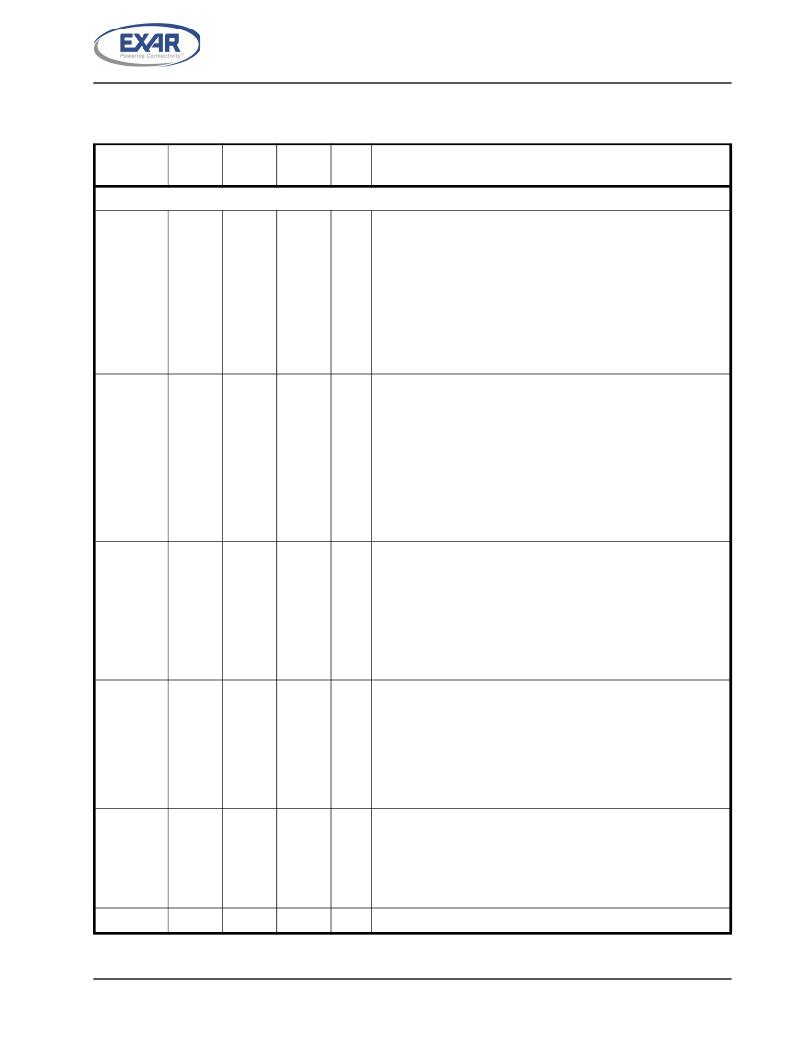

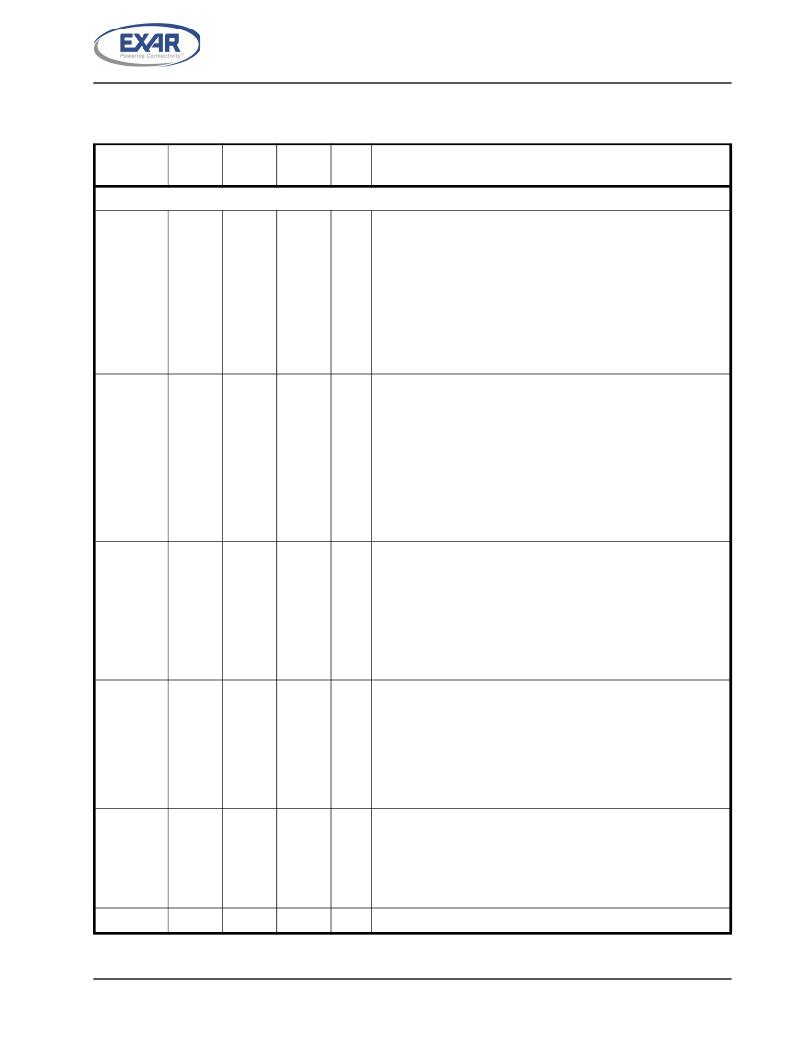

�PIN� DESCRIPTIONS�

�Pin� Description�

�UART� WITH� 128-BYTE� FIFO� AND� INTEGRATED� LEVEL� SHIFTERS�

�N� AME�

�QFN-32�

�P� IN� #�

�QFN-40� TQFP-48�

�PIN#� PIN#�

�T� YPE�

�D� ESCRIPTION�

�DATA� BUS� INTERFACE� -� Intel/Motorola�

�16/68#�

�32�

�1�

�1�

�I�

�Intel� or� Motorola� Bus� Select.� This� pin� selects� the� 16� or� 68� mode�

�when� VLIO_EN� is� a� logic� 0.� In� the� VLIO� mode� (VLIO_EN� is� a� logic�

�1),� this� pin� becomes� the� SLEEP/PWRDN#� pin� in� the� QFN-32� pack-�

�age.�

�When� 16/68#� pin� is� at� logic� 1,� 16� or� Intel� Mode,� the� device� will� oper-�

�ate� in� the� Intel� bus� type� of� interface.�

�When� 16/68#� pin� is� at� logic� 0,� 68� or� Motorola� mode,� the� device� will�

�operate� in� the� Motorola� bus� type� of� interface.� This� pin� does� not� have�

�an� internal� pull-up� or� pull-down� resistor.�

�A2�

�A1�

�A0�

�29�

�30�

�31�

�38�

�39�

�40�

�46�

�47�

�48�

�I�

�Address� lines� [2:0].� These� 3� address� lines� select� the� internal� regis-�

�ters� in� UART� channel� during� a� data� bus� transaction.�

�In� the� VLIO� bus� mode� (details� on� next� page):�

�■�

�■�

�■�

�■�

�A2� becomes� ENIR#�

�A1� becomes� ENRS485#� in� the� QFN-32� package�

�A1� is� an� unused� input� on� the� TQFP-48� and� QFN-40�

�packages� and� should� be� connected� to� GND�

�A0� becomes� LLA#�

�D7�

�D6�

�D5�

�D4�

�D3�

�D2�

�D1�

�D0�

�IOR#�

�8�

�7�

�6�

�5�

�4�

�3�

�2�

�1�

�13�

�9�

�8�

�7�

�6�

�5�

�4�

�3�

�2�

�16�

�9�

�8�

�7�

�6�

�5�

�4�

�3�

�2�

�10�

�I/O�

�I�

�Data� bus� lines� [7:0]� (bidirectional).�

�In� the� VLIO� bus� mode,� D7:D0� becomes� AD7:AD0.�

�When� 16/68#� pin� is� at� logic� 1,� the� Intel� bus� interface� is� selected� and�

�this� input� becomes� read� strobe� (active� low).� The� falling� edge� insti-�

�gates� an� internal� read� cycle� and� retrieves� the� data� byte� from� an�

�internal� register� pointed� by� the� address� lines� [A2:A0],� puts� the� data�

�byte� on� the� data� bus� to� allow� the� host� processor� to� read� it� on� the� ris-�

�ing� edge.�

�When� 16/68#� pin� is� at� logic� 0,� the� Motorola� bus� interface� is� selected�

�and� this� input� should� be� connected� to� VCC.�

�IOW#�

�14�

�17�

�11�

�I�

�When� 16/68#� pin� is� at� logic� 1,� it� selects� Intel� bus� interface� and� this�

�(R/W#)�

�input� becomes� write� strobe� (active� low).� The� falling� edge� instigates�

�the� internal� write� cycle� and� the� rising� edge� transfers� the� data� byte�

�on� the� data� bus� to� an� internal� register� pointed� by� the� address� lines.�

�When� 16/68#� pin� is� at� logic� 0,� the� Motorola� bus� interface� is� selected�

�and� this� input� becomes� read� (logic� 1)� and� write� (logic� 0)� signal.�

�CS#�

�15�

�18�

�12�

�I�

�This� input� is� chip� select� (active� low)� to� enable� the� device.�

�5�

�相关PDF资料 |

PDF描述 |

|---|---|

| RCC15DRTN-S13 | CONN EDGECARD 30POS .100 EXTEND |

| V150B3V3E100BL | CONVERTER MOD DC/DC 3.3V 100W |

| RCC06DRTN-S734 | CONN EDGECARD 12POS DIP .100 SLD |

| XR16M890IL40-0C-EB | BOARD EVAL XR16M890IL40 |

| M3CCA-1060K | IDC CABLE - MKC10A/MC10F/MKC10A |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR16M890IM48-F | 功能描述:UART 接口集成电路 1-Ch 8 Bit/VLIO UART w/Lvl Shftrs &16GPIO RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR16M890IM48TR | 制造商:EXAR 制造商全称:EXAR 功能描述:UART WITH 128-BYTE FIFO AND INTEGRATED LEVEL SHIFTERS |

| XR16M890IM48TR-F | 功能描述:UART 接口集成电路 1-Ch 8 Bit/VLIO UART w/Lvl Shftrs &16GPIO RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR16V2550 | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 16-BYTE FIFO |

| XR16V2550_07 | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 16-BYTE FIFO |

发布紧急采购,3分钟左右您将得到回复。