- 您现在的位置:买卖IC网 > PDF目录16524 > XR16V2550IM-0B-EB (Exar Corporation)EVAL BOARD FOR V2550 48TQFP PDF资料下载

参数资料

| 型号: | XR16V2550IM-0B-EB |

| 厂商: | Exar Corporation |

| 文件页数: | 4/46页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR V2550 48TQFP |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

XR16V2550

12

HIGH PERFORMANCE DUART WITH 16-BYTE FIFO

REV. 1.0.3

2.11

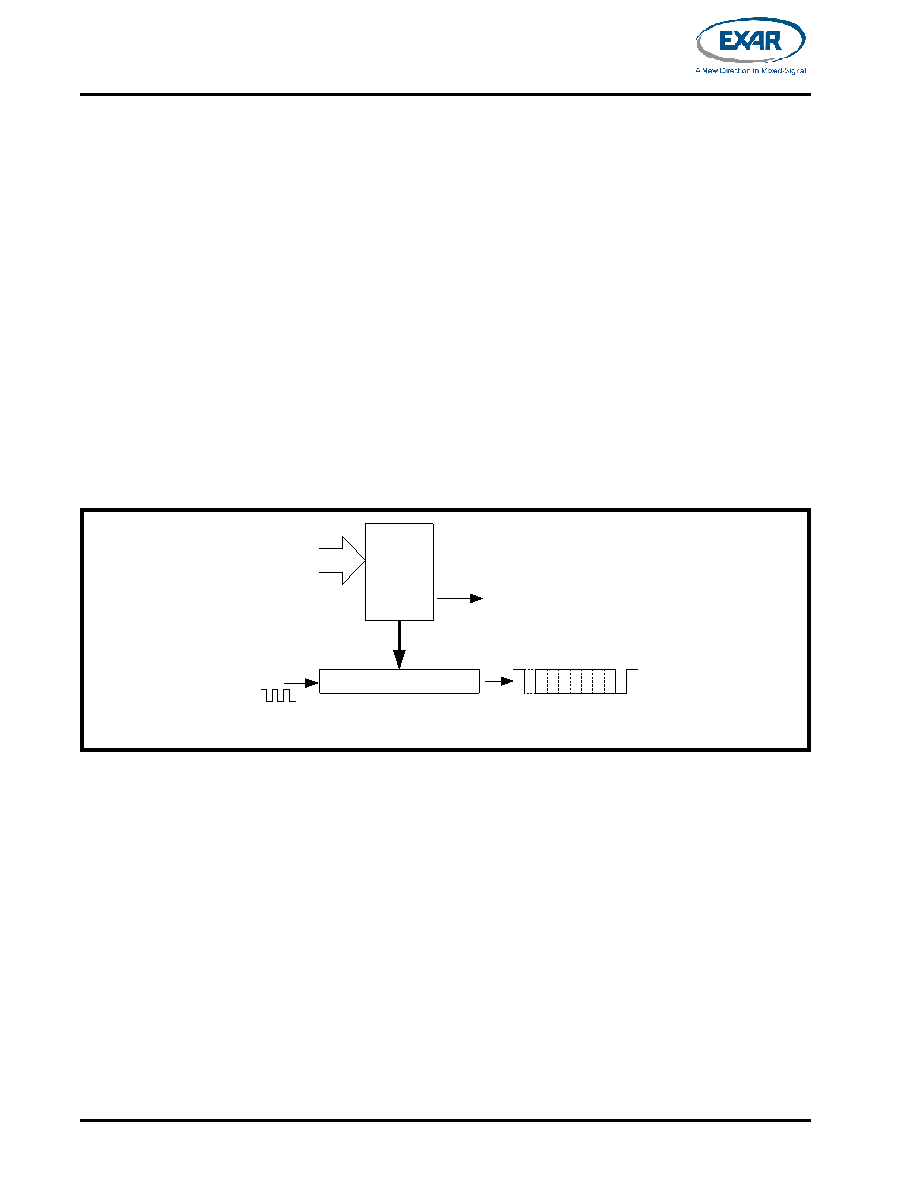

Transmitter

The transmitter section comprises of an 8-bit Transmit Shift Register (TSR) and 16 bytes of FIFO which

includes a byte-wide Transmit Holding Register (THR). TSR shifts out every data bit with the 16X/8X/4X

internal clock. A bit time is 16/8/4 clock periods (see DLD). The transmitter sends the start-bit followed by the

number of data bits, inserts the proper parity-bit if enabled, and adds the stop-bit(s). The status of the FIFO and

TSR are reported in the Line Status Register (LSR bit-5 and bit-6).

2.11.1

Transmit Holding Register (THR) - Write Only

The transmit holding register is an 8-bit register providing a data interface to the host processor. The host

writes transmit data byte to the THR to be converted into a serial data stream including start-bit, data bits,

parity-bit and stop-bit(s). The least-significant-bit (Bit-0) becomes first data bit to go out. The THR is the input

register to the transmit FIFO of 16 bytes when FIFO operation is enabled by FCR bit-0. Every time a write

operation is made to the THR, the FIFO data pointer is automatically bumped to the next sequential data

location.

2.11.2

Transmitter Operation in non-FIFO Mode

The host loads transmit data to THR one character at a time. The THR empty flag (LSR bit-5) is set when the

data byte is transferred to TSR. THR flag can generate a transmit empty interrupt (ISR bit-1) when it is enabled

by IER bit-1. The TSR flag (LSR bit-6) is set when TSR becomes completely empty.

FIGURE 6. TRANSMITTER OPERATION IN NON-FIFO MODE

Transmit

Holding

Register

(THR)

Transmit Shift Register (TSR)

Data

Byte

L

S

B

M

S

B

THR Interrupt (ISR bit-1)

Enabled by IER bit-1

TXNOFIFO1

16X or 8X or 4X

Clock

( DLD[5:4] )

2.11.3

Transmitter Operation in FIFO Mode

The host may fill the transmit FIFO with up to 16 bytes of transmit data. The THR empty flag (LSR bit-5) is set

whenever the FIFO is empty. The THR empty flag can generate a transmit empty interrupt (ISR bit-1) when the

amount of data in the FIFO falls below its selected trigger level. The transmit empty interrupt is enabled by IER

bit-1. The TSR flag (LSR bit-6) is set when TSR/FIFO becomes empty.

相关PDF资料 |

PDF描述 |

|---|---|

| GCA22DCBH | CONN EDGECARD 44POS R/A .125 SLD |

| GEM36DTBH | CONN EDGECARD 72POS R/A .156 SLD |

| GCA22DCBD | CONN EDGECARD 44POS R/A .125 SLD |

| GEM36DTBD | CONN EDGECARD 72POS R/A .156 SLD |

| UPJ1J560MPD6TD | CAP ALUM 56UF 63V 20% RADIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR16V2550IM-F | 功能描述:UART 接口集成电路 2.5V-3.6V 16B FIFO temp -45 to 85C;UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR16V2550IMTR-F | 制造商:Exar Corporation 功能描述:UART 2-CH 16Byte FIFO 2.5V/3.3V 48-Pin TQFP T/R 制造商:Exar Corporation 功能描述:XR16V2550IMTR-F |

| XR16V2551 | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 16-BYTE FIFO AND POWERSAVE FEATURE |

| XR16V2551_07 | 制造商:EXAR 制造商全称:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 16-BYTE FIFO AND POWERSAVE FEATURE |

| XR16V2551IL | 制造商:Rochester Electronics LLC 功能描述: 制造商:Exar Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。