- 您现在的位置:买卖IC网 > PDF目录16491 > XR16V654DIV-0A-EB (Exar Corporation)EVAL BOARD FOR XR16V654D 64LQFP PDF资料下载

参数资料

| 型号: | XR16V654DIV-0A-EB |

| 厂商: | Exar Corporation |

| 文件页数: | 13/58页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR16V654D 64LQFP |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

XR16V654/654D

20

2.25V TO 3.6V QUAD UART WITH 64-BYTE FIFO

REV. 1.0.1

2.11

Auto RTS (Hardware) Flow Control

Automatic RTS hardware flow control is used to prevent data overrun to the local receiver FIFO. The RTS#

output is used to request remote unit to suspend/resume data transmission. The auto RTS flow control

features is enabled to fit specific application requirement (see Figure 12):

Enable auto RTS flow control using EFR bit-6.

The auto RTS function must be started by asserting RTS# output pin (MCR bit-1 to logic 1 after it is enabled).

If using the Auto RTS interrupt:

Enable RTS interrupt through IER bit-6 (after setting EFR bit-4). The UART issues an interrupt when the RTS#

pin makes a transition from low to high: ISR bit-5 will be set to logic 1.

2.12

Auto RTS Hysteresis

The V654 has a new feature that provides flow control trigger hysteresis while maintaining compatibility with

the XR16C850, ST16C650A and ST16C550 family of UARTs. With the Auto RTS function enabled, an interrupt

is generated when the receive FIFO reaches the selected RX trigger level. The RTS# pin will not be forced

HIGH (RTS off) until the receive FIFO reaches one trigger level above the selected trigger level in the trigger

table (Table 12). The RTS# pin will return LOW after the RX FIFO is unloaded to one level below the selected

trigger level. Under the above described conditions, the V654 will continue to accept data until the receive

FIFO gets full. The Auto RTS function is initiated when the RTS# output pin is asserted LOW (RTS On).

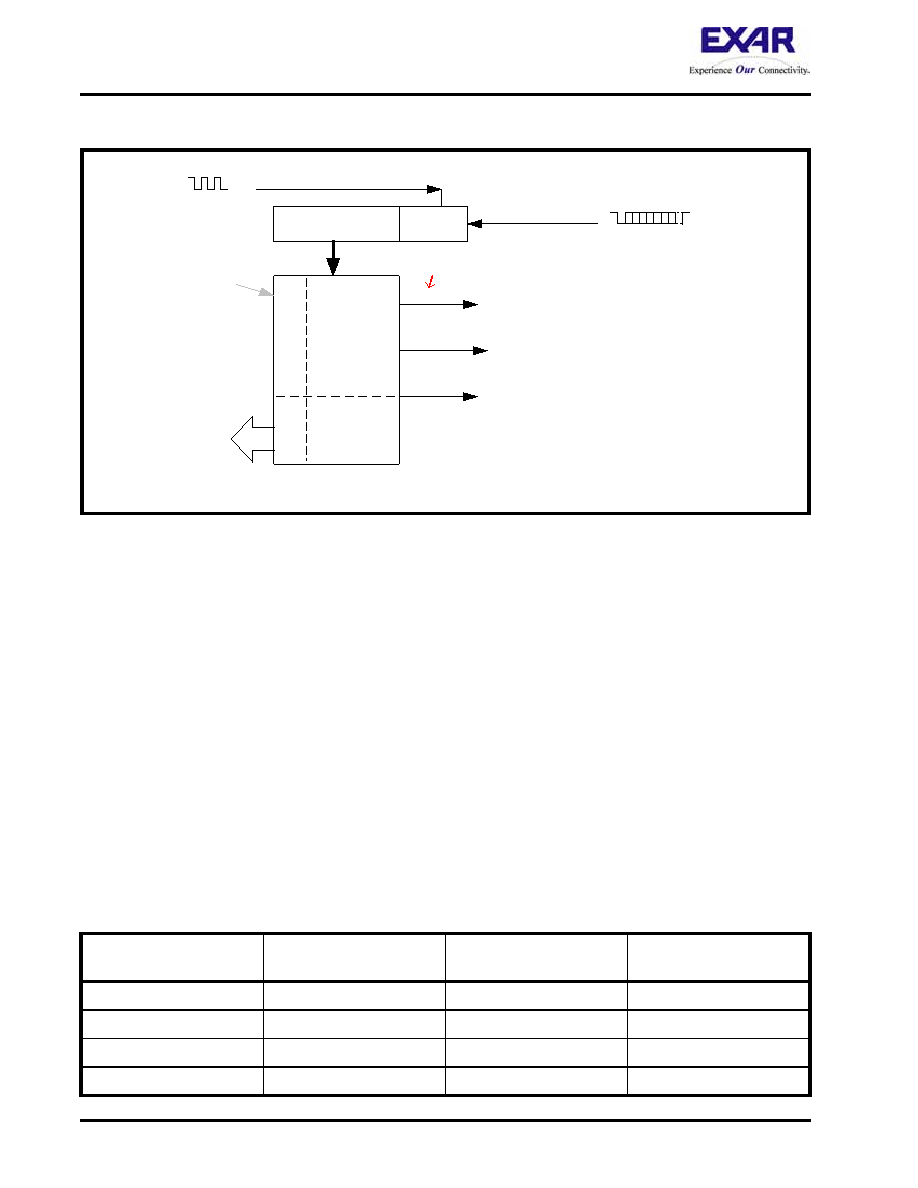

FIGURE 11. RECEIVER OPERATION IN FIFO AND AUTO RTS FLOW CONTROL MODE

TABLE 7: AUTO RTS (HARDWARE) FLOW CONTROL

RX TRIGGER LEVEL

INT PIN ACTIVATION

RTS# DE-ASSERTED (HIGH)

(CHARACTERS IN RX FIFO)

RTS# ASSERTED (LOW)

(CHARACTERS IN RX FIFO)

8

16

0

16

56

8

56

60

16

60

56

Receive Data S hift

R egister (R S R )

R X FIFO 1

16X or 8X or 4X C lock

( DLD[5:4] )

Err

o

rT

a

g

s

(64

-se

ts

)

Er

ro

rT

a

g

s

i

n

LS

R

b

it

s

4:

2

R eceive D ata C haracters

D ata B it

V alidation

Receive

D ata FIF O

Receive

Data

Receive Data

B yte and E rrors

R H R Interrupt (IS R bit-2) program m ed for

desired FIFO trigger level.

FIFO is E nabled by F C R bit-0=1

R TS # de-asserts w hen data fills above the flow

control trigger level to suspend rem ote transm itter.

E nable by E FR bit-6=1, M C R bit-1.

R TS# re-asserts w hen data falls below the flow

control trigger level to restart rem ote transm itter.

E nable by E FR bit-6=1, M C R bit-1.

64 bytes by 11-bit w ide

FIFO

Trigger=16

D ata falls to

8

D ata fills to

56

E xam ple

: - R X FIFO trigger level selected at 16 bytes

(See N ote Below )

相关PDF资料 |

PDF描述 |

|---|---|

| USR0J330MDD | CAP ALUM 33UF 6.3V 20% RADIAL |

| XR16V564IV80-0A-EB | EVAL BOARD FOR XR16V564 80LQFP |

| ECM18DRXH | CONN EDGECARD 36POS DIP .156 SLD |

| A3932SEQ | IC CTRLR MOSFET 3PH 32-PLCC |

| RPP30-4824SW | CONV DC/DC 30W 18-75VIN 24VOUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR16V654DIV-F | 功能描述:UART 接口集成电路 UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR16V654DIVTR-F | 制造商:Exar Corporation 功能描述:UART 4-CH 64Byte FIFO 2.5V/3.3V 64-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR16V654DIVTR-F |

| XR16V654IJ | 制造商:Rochester Electronics LLC 功能描述: 制造商:Exar Corporation 功能描述: |

| XR16V654IJ-0A-EVB | 功能描述:UART 接口集成电路 Supports V654 68 ld PLCC, ISA Interface RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR16V654IJ-F | 功能描述:UART 接口集成电路 UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。