- 您现在的位置:买卖IC网 > PDF目录16820 > XR17V358IB-E8-EVB (Exar Corporation)EVAL BOARD FOR XR17V358-E8 PDF资料下载

参数资料

| 型号: | XR17V358IB-E8-EVB |

| 厂商: | Exar Corporation |

| 文件页数: | 4/68页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR17V358-E8 |

| 产品培训模块: | PCIe UARTs UART Product Overview |

| 标准包装: | 1 |

| 主要目的: | 接口,UART |

| 嵌入式: | 否 |

| 已用 IC / 零件: | XR17V358 |

| 已供物品: | 板 |

| 相关产品: | 1016-1294-ND - IC UART PCIE OCTAL 176FPBGA |

| 其它名称: | 1016-1296 |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

XR17V358

12

HIGH PERFORMANCE OCTAL PCI EXPRESS UART

REV. 1.0.4

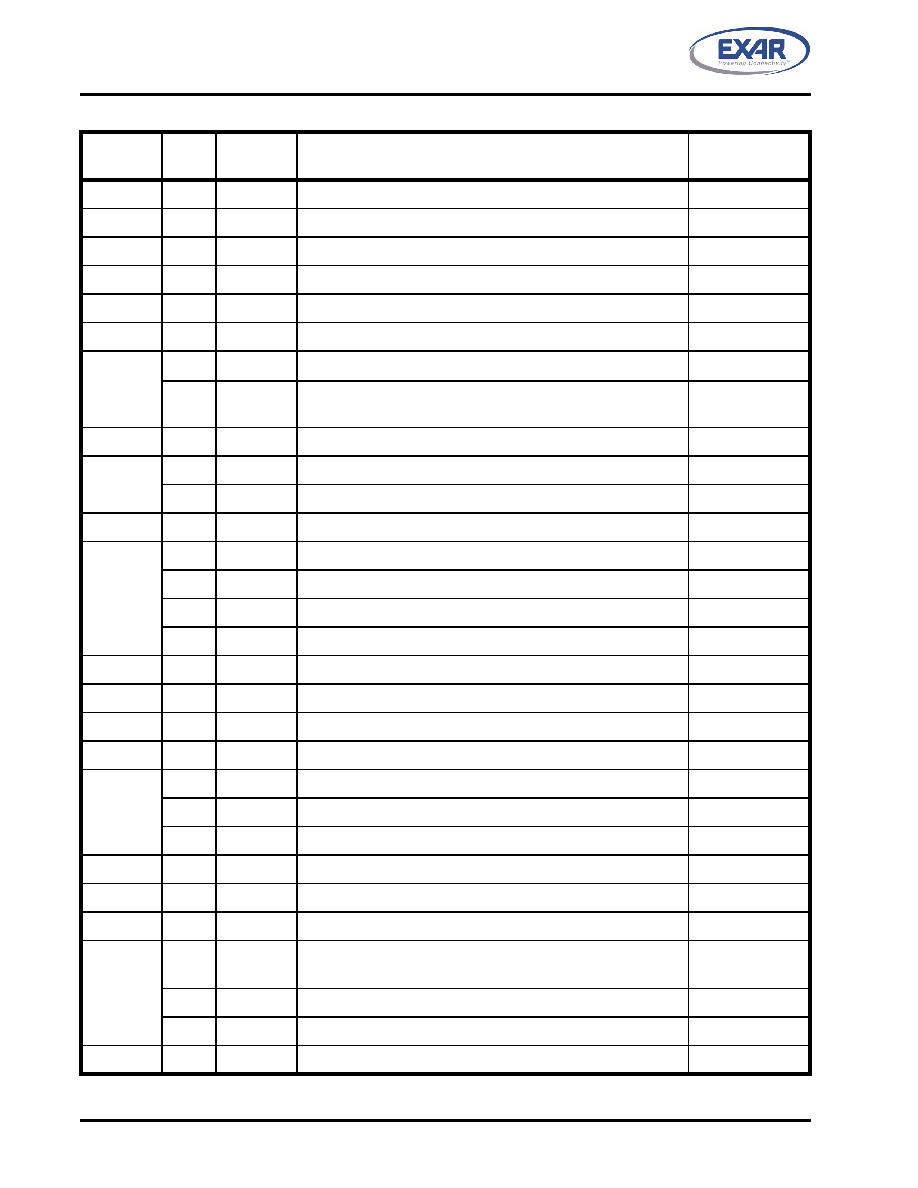

0x14

31:0

RWR

Unimplemented Base Address Register (returns zeros)

0x00000000

0x18h

31:0

RO

Unimplemented Base Address Register (returns zeros)

0x00000000

0x1C

31:0

RO

Unimplemented Base Address Register (returns zeros)

0x00000000

0x20

31:0

RO

Unimplemented Base Address Register (returns zeros)

0x00000000

0x24

31:0

RO

Unimplemented Base Address Register (returns zeros)

0x00000000

0x28

31:0

RO

Reserved

0x00000000

0x2C

31:16

EWR

Subsystem ID (write from external EEPROM by customer)

0x0000

15:0

EWR

Subsystem Vendor ID (write from external EEPROM by cus-

tomer)

0x0000

0x30

31:0

RO

Expansion ROM Base Address (Unimplemented)

0x00000000

0x34

31:8

RO

Reserved (returns zeros)

0x000000

7:0

RO

Capability Pointer

0x50

0x38

31:0

RO

Reserved (returns zeros)

0x00000000

0x3C

31:24

RO

Unimplemented MAXLAT

0x00

23:16

RO

Unimplemented MINGNT

0x00

15:8

RO

Interrupt Pin, use INTA#.

0x01

7:0

RWR

Interrupt Line.

0xXX

0x40

31:0

RO

Not implemented or not applicable (return zeros)

0x00000000

0x44

31:0

RO

CSR

0x02106160

0x48

31:0

RO

Not implemented or not applicable (return zeros)

0x00000000

0x4C

31:0

RO

Not implemented or not applicable (return zeros)

0x00000000

0x50

31:16

RO

64-bit address capable

0x0080

15:8

RO

Next Capability Pointer

0x78

7:0

RO

MSI Capable Capability ID

0x05

0x54-0x67 31:0

RO

Not implemented or not applicable (return zeros)

0x00000000

0x68

31:0

RO

Not implemented or not applicable

0x0000xxxx

0x6C-0x77 31:0

RO

Not implemented or not applicable (return zeros)

0x00000000

0x78

31:16

RO

PME# support (PME# can be asserted from D3hot and D0)

PCI Power Management 1.2

0x4803

15:8

RO

Next Capability Pointer

0x80

7:0

RO

Power Management Capability ID

0x01

0x7C

31:0

RO

No soft reset when transitioning from D3hot to D0 state

0x00000008

TABLE 1: PCI LOCAL BUS CONFIGURATION SPACE REGISTERS

ADDRESS

OFFSET

BITS

TYPE

DESCRIPTION

RESET VALUE

(HEX OR BINARY)

相关PDF资料 |

PDF描述 |

|---|---|

| EBM24DCSH-S288 | CONN EDGECARD 48POS .156 EXTEND |

| EGM08DRST | CONN EDGECARD 16POS DIP .156 SLD |

| V150B28E150BL | CONVERTER MOD DC/DC 28V 150W |

| HSM06DRYH-S13 | CONN EDGECARD 12POS .156 EXTEND |

| EBM24DCSD-S288 | CONN EDGECARD 48POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR1857SN | 制造商:Electro-Term/Hollingsworth 功能描述: |

| XR1858SN | 制造商:Electro-Term/Hollingsworth 功能描述: |

| XR1859SN | 制造商:Electro-Term/Hollingsworth 功能描述: |

| XR1859SNT | 制造商:Hollingsworth 功能描述: |

| XR1880S | 制造商:Electro-Term/Hollingsworth 功能描述: |

发布紧急采购,3分钟左右您将得到回复。