参数资料

| 型号: | XR68M752IM48-F |

| 厂商: | Exar Corporation |

| 文件页数: | 8/54页 |

| 文件大小: | 0K |

| 描述: | IC UART FIFO 64B DUAL 48TQFP |

| 标准包装: | 250 |

| 特点: | * |

| 通道数: | 2,DUART |

| FIFO's: | 64 字节 |

| 规程: | RS232,RS422,RS485 |

| 电源电压: | 1.62 V ~ 3.63 V |

| 带自动流量控制功能: | 是 |

| 带IrDA 编码器/解码器: | 是 |

| 带故障启动位检测功能: | 是 |

| 带调制解调器控制功能: | 是 |

| 带CMOS: | 是 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-TQFP |

| 供应商设备封装: | 48-TQFP(7x7) |

| 包装: | 托盘 |

| 其它名称: | 1016-1479 1016-1479-ND 1016-1642 XR68M752IM48-F-ND |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页

XR16M752/XR68M752

16

HIGH PERFORMANCE DUART WITH 64-BYTE FIFO

REV. 1.1.1

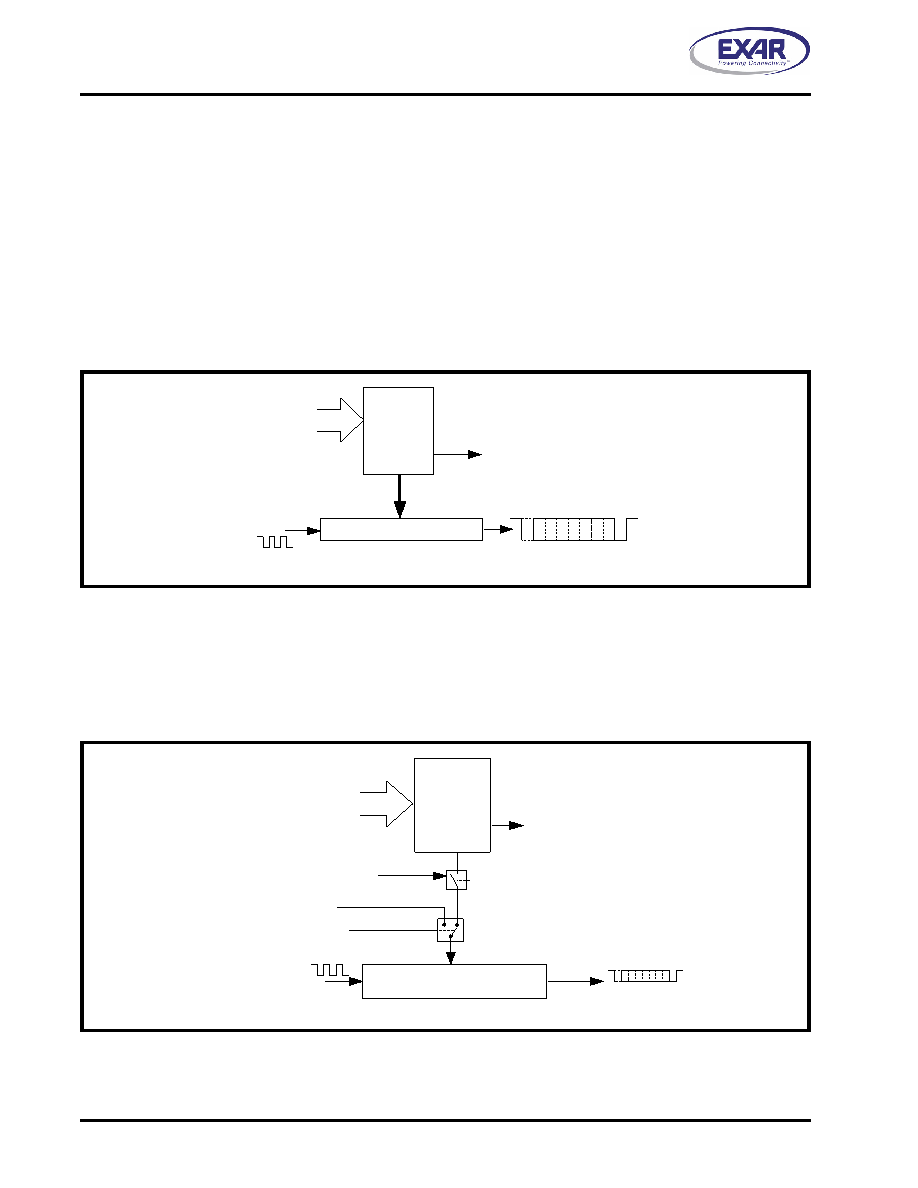

2.9.1

Transmit Holding Register (THR) - Write Only

The transmit holding register is an 8-bit register providing a data interface to the host processor. The host

writes transmit data byte to the THR to be converted into a serial data stream including start-bit, data bits,

parity-bit and stop-bit(s). The least-significant-bit (Bit-0) becomes first data bit to go out. The THR is the input

register to the transmit FIFO of 64 bytes when FIFO operation is enabled by FCR bit-0. Every time a write

operation is made to the THR, the FIFO data pointer is automatically bumped to the next sequential data

location.

2.9.2

Transmitter Operation in non-FIFO Mode

The host loads transmit data to THR one character at a time. The THR empty flag (LSR bit-5) is set when the

data byte is transferred to TSR. THR flag can generate a transmit empty interrupt (ISR bit-1) when it is enabled

by IER bit-1. The TSR flag (LSR bit-6) is set when TSR becomes completely empty.

FIGURE 7. TRANSMITTER OPERATION IN NON-FIFO MODE

Transmit

Holding

Register

(THR)

Transmit Shift Register (TSR)

Data

Byte

L

S

B

M

S

B

THR Interrupt (ISR bit-1)

Enabled by IER bit-1

TXNOFIFO1

16X or 8X or 4X

Clock

( DLD[5:4] )

2.9.3

Transmitter Operation in FIFO Mode

The host may fill the transmit FIFO with up to 64 bytes of transmit data. The THR empty flag (LSR bit-5) is set

whenever the FIFO is empty. The THR empty flag can generate a transmit empty interrupt (ISR bit-1) when the

amount of data in the FIFO falls below its programmed trigger level. The transmit empty interrupt is enabled by

IER bit-1. The TSR flag (LSR bit-6) is set when TSR/FIFO becomes empty.

FIGURE 8. TRANSMITTER OPERATION IN FIFO AND FLOW CONTROL MODE

Transmit Data Shift Register

(TSR)

Transmit

Data Byte

THR Interrupt (ISR bit-1) falls

below the programmed Trigger

Level and then when becomes

empty. FIFO is Enabled by FCR

bit-0=1

Transmit

FIFO

16X or 8X or 4X Clock

( DLD[5:4] )

Auto CTS Flow Control (CTS# pin)

Auto Software Flow Control

Flow Control Characters

(Xoff1/2 and Xon1/2 Reg.)

TXFIFO 1

相关PDF资料 |

PDF描述 |

|---|---|

| XR16M752IM48-F | IC UART FIFO 34B DUAL 48TQFP |

| ST16C450CQ48-F | IC UART SINGLE 48TQFP |

| ST16C2450IQ48-F | IC UART FIFO DUAL 48TQFP |

| MAX7314AEG+T | IC I/O EXPANDER I2C 16B 24QSOP |

| ST16C550IQ48-F | IC UART FIFO 16B SGL 48TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR68M752IM48TR-F | 制造商:Exar Corporation 功能描述:XR68M752 Series 16 Mbps High Performance DUART With 64-Byte FIFO - TQFP-48 |

| XR7090AA-BC-0001 | 制造商:CREE 制造商全称:Cree, Inc 功能描述:XLamp㈢ XR LED Binning and Labeling |

| XR7090AA-BC-DD-EF-G-HHHH | 制造商:CREE 制造商全称:Cree, Inc 功能描述:XLamp㈢ XR LED Binning and Labeling |

| XR7090-AM-L1-0001 | 制造商:Cree 功能描述:LED AMBER XR 制造商:Cree 功能描述:LED, AMBER, XR 制造商:Cree 功能描述:LED, HIGH BRIGHTNESS, RED ORANGE, 67.2LM; Series:XLamp XR; LED Color:Amber; Luminous Flux @ Test:42lm; Wavelength Typ:595nm; Forward Current @ Test:350mA; Forward Current If Max:700mA; Forward Voltage @ Test:2.25V; Viewing Angle:100;RoHS Compliant: Yes |

| XR7090AM-L1-0001 | 制造商:Cree 功能描述:LED Uni-Color Amber 2-Pin SMD |

发布紧急采购,3分钟左右您将得到回复。