- 您现在的位置:买卖IC网 > PDF目录11815 > XR88C681P/40 (Exar Corporation)IC UART CMOS DUAL 40PDIP PDF资料下载

参数资料

| 型号: | XR88C681P/40 |

| 厂商: | Exar Corporation |

| 文件页数: | 18/101页 |

| 文件大小: | 0K |

| 描述: | IC UART CMOS DUAL 40PDIP |

| 产品变化通告: | Leaded UART, V&I Obsolescence 11/Apr/2011 |

| 标准包装: | 9 |

| 特点: | * |

| 通道数: | 2,DUART |

| FIFO's: | 1 字节,3 字节 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 带并行端口: | 是 |

| 带CMOS: | 是 |

| 安装类型: | 通孔 |

| 封装/外壳: | 40-DIP(0.600",15.24mm) |

| 供应商设备封装: | 40-PDIP |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页

XR88C681

23

Rev. 2.11

program control to a specific location in system memory.

For CPUs that employ direct interrupts, this “location” is

fixed by the CPU circuitry itself.

For Example:

If the -INT0 interrupt request input pin, of the 8051 C, is

asserted, the CPU will branch program control to location

000316 in system memory. This location is fixed (by circuit

design of the 8051 P) and cannot be changed by the

user.

(External) Vectored Interrupt Processing

CPUs that employ this form of interrupt processing

typically have an Interrupt Acknowledge output pin. This

“IACK” or “-INTA” output will be used to gate “interrupt

vector” information onto the Data Bus, via external

(non-DUART) hardware. The term “External” is used to

describe this form of vectored-interrupt processing;

because the location of the interrupt service routine is

determined by hardware “external” to the DUART. For

some CPUs, (such as the 8080A and the 8085 P), this

“interrupt vector” information is a one byte op-code for a

CALL instruction to a special “RESTART subroutine”.

The location of this “RESTART subroutine” is fixed by

CPU circuit design. If the user employs this approach for

interrupt processing, he/she is responsible for insuring

that either the interrupt service routine, or an

unconditional branch instruction (to the interrupt service

routine) resides at this location in memory.

Each of these Interrupt Processing techniques will be

presented in greater detail in the following sections.

As mentioned earlier, the DUART should be operating in

the I-Mode, when interfaced to the P/ C presented in

Table 7. Table 7 also presents the type of interrupt

processing that is employed by each of these Ps/ Cs.

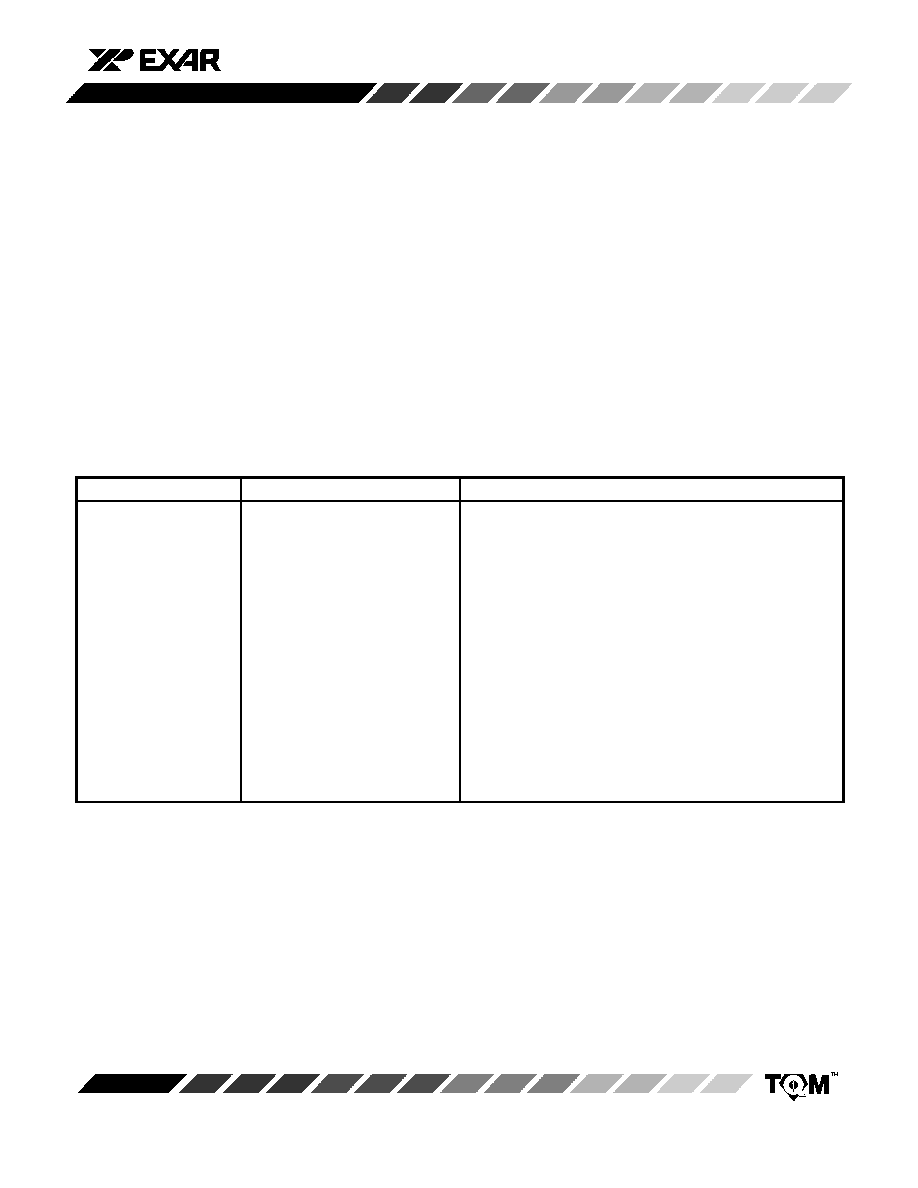

P/ C

Type of Interrupt Processing

Comments

8051 C

Direct

The 8051 C has two external Interrupt Request inputs: -INT0

and -INT1.

8080A P

External Vectored

The 8080A P will allow the use of up to 8 different op codes

for

“CALL” instructions to the Interrupt Service Routines.

The 8080A CPU module will output an interrupt ac-

knowledge output, -INTA, which can be used to “gate”

the “CALL” instructions on to the Data Bus.

8085 P

Direct and External Vectored

The 8085 P has three “Direct” external Interrupt Request

inputs: RST 7.5, RST 6.5, and RST 5.5. Additionally, this P

has the exact same “vector” options as does the 8080A P.

68HC11 C

Direct

The 68HC11 C has a single “maskable” external Interrupt

Request input; -IRQ.

Z-80 P

(Interrupt Mode 0)

External Vectored

The Z-80 CPU uses the exact same approach as presented

for the 8080A CPU.

Z-80 P

Direct Interrupt

The Z-80 will branch to 0038H in system memory if the -INT

interrupt request pin is asserted.

Table 7. Summary of P/ C and their types of Interrupt Processing (I - Mode)

The information presented in

Table 7 is discussed in detail in the following sections.

相关PDF资料 |

PDF描述 |

|---|---|

| V24B24H150BG2 | CONVERTER MOD DC/DC 24V 150W |

| XR88C681CP/40 | IC UART CMOS DUAL 40PDIP |

| XR68C681P | IC UART CMOS DUAL 40PDIP |

| XR68C681CP | IC UART CMOS DUAL 40PDIP |

| V24B24H150BG | CONVERTER MOD DC/DC 24V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR88C681XR101524CNN | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| XR88C681XR101524M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| XR88C681XR101524N | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| XR88C681XR101528CJJ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| XR88C681XR101528CNN | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

发布紧急采购,3分钟左右您将得到回复。